**General Information**

**FPGA Data Sheets**

REVOLUTIONIZING THE **FPGA INDUSTRY**

**CAE Design Tools**

**Application Notes**

Quality, Reliability, and Packaging Information

**Papers and Article Reprints**

**Sales Representatives and Distributors**

QuickLogic Corporation 2933 Bunker Hill Lane Santa Clara, CA 95054

General Information (408) 987-2000 Applications Hotline (408) 987-2100 FAX: (408) 987-2012 EMAIL: info@qlogic.com

#### Copyright © 1992, 1995 QuickLogic Corporation

pASIC®, Vialink®, and QuickLogic® are registered trademarks and SpDE™, WildCat™ and QuickWorks™ are trademarks of QuickLogic Corporation

QuickLogic Corporation acknowledges the trademarks of other organizations for their respective products or services mentioned in this databook, including:

PAL® and Palasm® are registered trademarks of Advanced Micro Devices Verilog® is a registered trademark and Concept™ is a trademark of Cadence Design Systems, Inc.

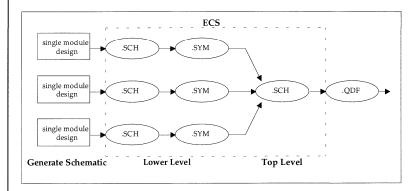

Data I/O<sup>®</sup> is a registered trademark and Synario<sup>™</sup>, ABEL<sup>™</sup>, and ECS<sup>™</sup> are trademarks of Data I/O Corporation

PowerPC™ is a trademark of IBM Corporation

Pentium™ is a trademark of Intel Corporation

SmartModel® is a registered trademark of Logic Modeling Corporation

MSDOS® and Microsoft® are registered trademarks and Windows™ is a trademark of Microsoft Corporation

Motif® is a registered trademark of Open Software Foundation

Sun Workstation™ is a trademark of Sun Microsystems

Synopsys® is a registered trademark and Design Compiler™ is a trademark of Synopsys, Inc.

ViewLogic®, Workview®, ViewDraw®, and ViewSim® are registered trademarks of ViewLogic Systems, Inc.

#### Life Support Policy

QuickLogic's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and the President of QuickLogic.

- Life support devices or systems are devices which (a) are intended for surgical

implant into the body or (b) support or sustain life and whose failure to perform,

when properly used in accordance with instructions for use provided in the

labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or affect its safety or effectiveness.

QuickLogic does not assume any liability resulting from the application or use of any product described within. No circuit patent licenses are implied. QuickLogic Corporation reserves the right to make changes without notice to any product herein to improve reliability, function, or design.

Products mentioned in this databook are covered by one or more of the following US

5,196,724; 5,122,685; 5,220,213; 5,243,226; 5,280,202; 5,362,676;

5,319,238; 5,302,546; 5,327,024; 5,293,133; 5,294,846

Additional patents pending.

QuickLogic Corporation 2933 Bunker Hill Lane Santa Clara, CA 95054 Tel: 408-987-2000

Tel: 408-987-2000 Fax: 408-987-2012

Welcome to the 1995 edition of the QuickLogic Data Book.

New in this edition are:

- 1. 8,000 gate *Wild*Cat Series FPGAs featuring fully PCI 2.0 compliant input/output capability.

- 2. "L" series Low Power FPGA devices offering 3.3 Volt supply operation.

- 3. "-X" speed grade FPGAs for cost sensitive applications.

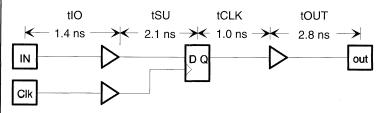

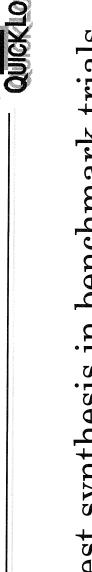

Also new is the 5.0 release of our SpDE design tools and the new Quick Works toolset which includes:

- Verilog® / VHDL Synthesis

- Context Sensitive HDL Editing

- Color Coded HDL Template Expansion

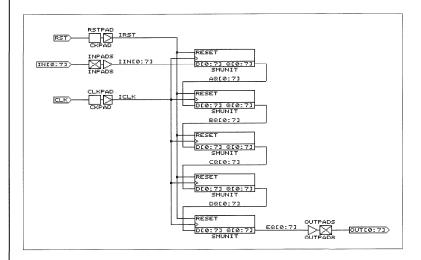

- Mixed-Mode Design Entry

- Enhanced Schematic Capture

- Comprehensive Verilog Simulation

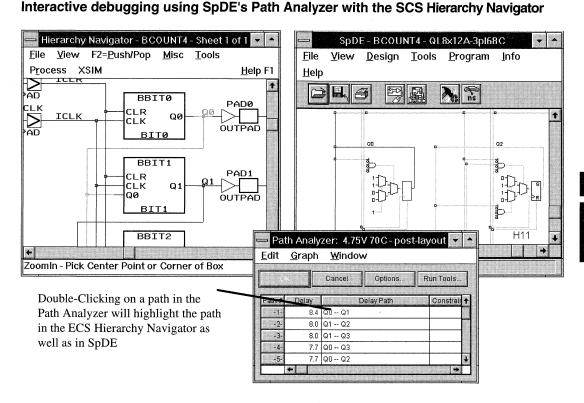

- Interactive Cross-Probing Between Tools

- Improved Logic Optimization

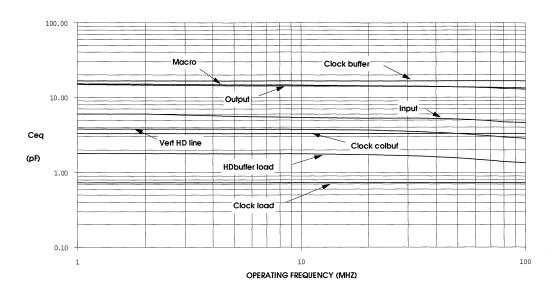

New information includes a Thermal Management section and upgrades to the Power vs Operating Frequency and Packagings sections.

QuickLogic's technology, architecture and design tools are revolutionizing the FPGA industry by solving the problems of traditional FPGAs.

For a QUICK response fax us at (408) 987-2012 or call us at 1-800-842-FPGA (3742) or email us at info@qlogic.comfor more information on QuickLogic products.

Thank you for your interest in QuickLogic and its products.

# **Table of Contents**

| Gene        | ral Information                                 |       |

|-------------|-------------------------------------------------|-------|

|             | Quick Reference Product Guide                   |       |

|             | Ordering Information                            |       |

|             | Family Overview                                 | 1-5   |

|             |                                                 |       |

|             |                                                 |       |

| <b>FPGA</b> | A Data Sheets                                   |       |

|             | pASIC 1 Family Data Sheet                       | 2-1   |

|             | QL8x12B WildCat 1000 (gate) FPGA                |       |

|             | QL12x16B WildCat 2000 (gate) FPGA               |       |

|             | QL16x24B WildCat 4000 (gate) FPGA               |       |

|             | QL24x32B <i>Wild</i> Cat 8000 (gate) FPGA       | .2-39 |

|             | QL8x12BL 3.3V WildCat 1000 (gate) FPGA          | .2-47 |

|             | QL12x16BL <i>3.3V Wild</i> Cat 2000 (gate) FPGA |       |

|             | QL16x24BL <i>3.3V Wild</i> Cat 4000 (gate) FPGA |       |

|             | QL24x32BL <i>3.3V Wild</i> Cat 8000 (gate) FPGA |       |

| 045         | Danima Tank                                     |       |

| CAE         | Design Tools                                    |       |

|             | pASIC Development Solutions                     |       |

|             | SpDE Tools                                      |       |

|             | QuickTools                                      |       |

|             | Quick Works Toolkit                             |       |

|             | Mentor Tools                                    |       |

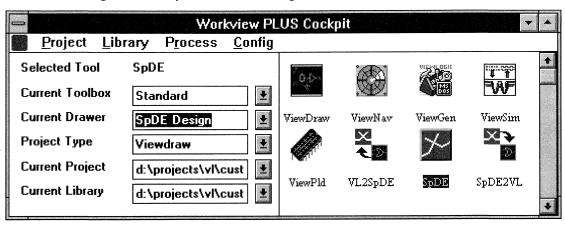

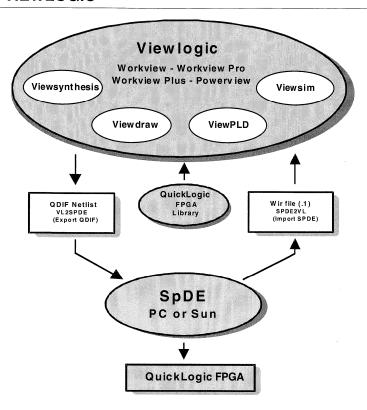

|             | Viewlogic Tools                                 | .3-15 |

|             | Intergraph Tools                                |       |

|             | Synopsys Tools                                  |       |

|             | Cadence Tools                                   |       |

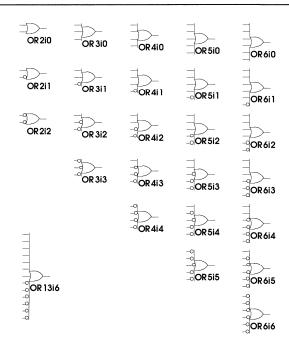

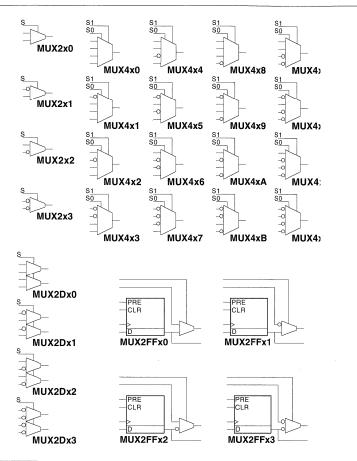

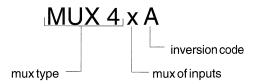

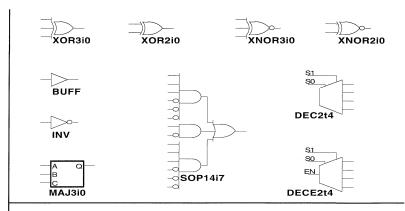

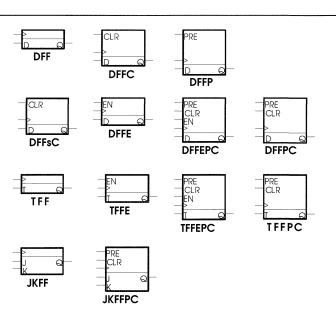

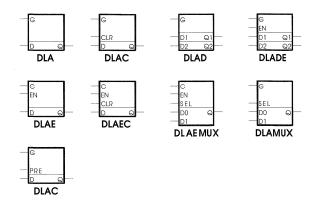

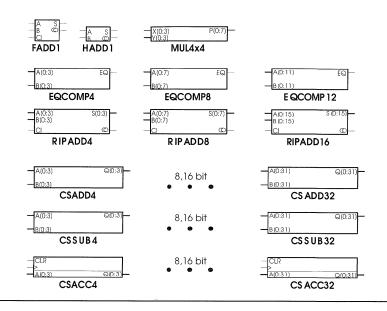

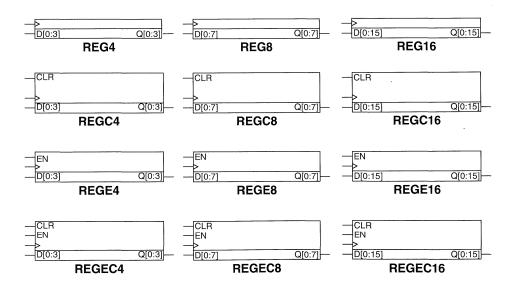

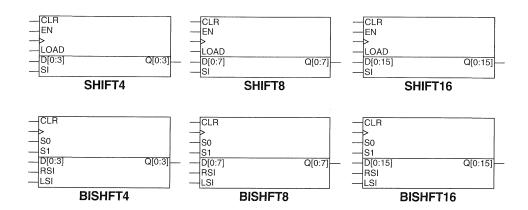

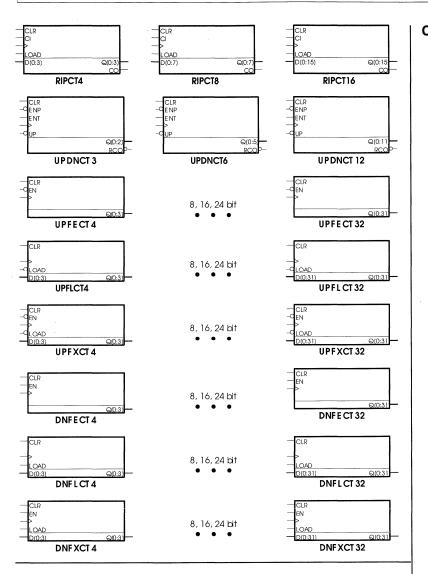

|             | pASIC Macro Library                             | .3-23 |

|             | Programming/Testing Toolkit                     | .3-37 |

|             | \$99 "Checkout Your Design in Our FPGA" Kit     |       |

|             | Third Party Support                             | .3-45 |

# TABLE OF CONTENTS

| Application | Notes |

|-------------|-------|

|-------------|-------|

|        | Application note summary                             | 4- <sup>-</sup>   |

|--------|------------------------------------------------------|-------------------|

|        | QAN1 Registers and Latches in the pASIC Architecture |                   |

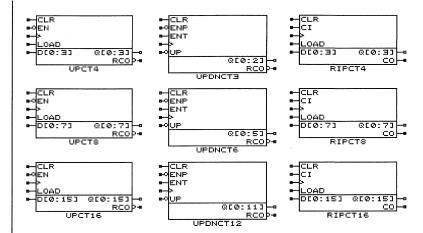

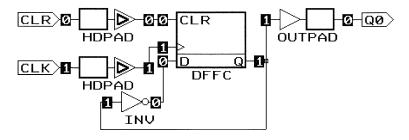

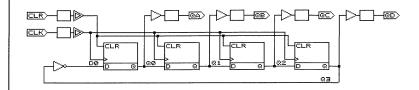

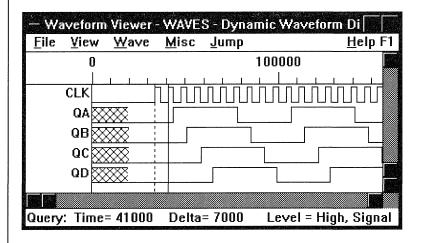

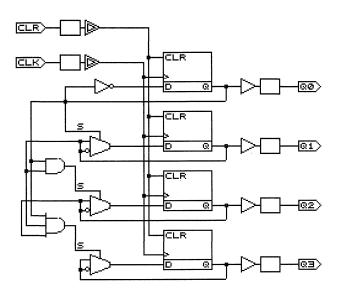

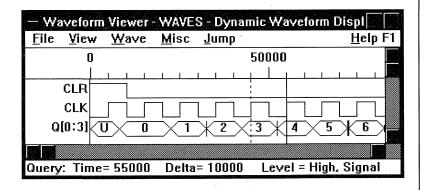

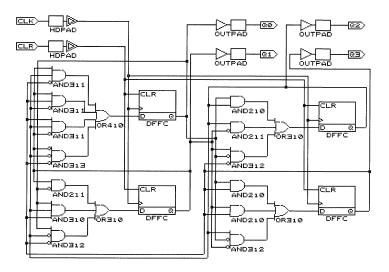

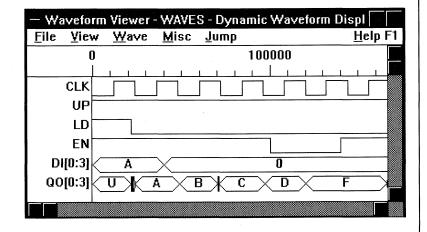

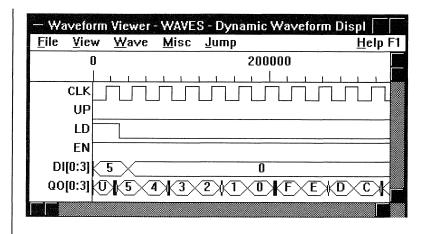

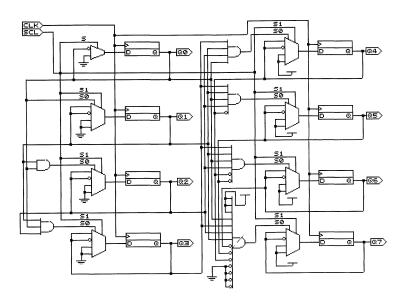

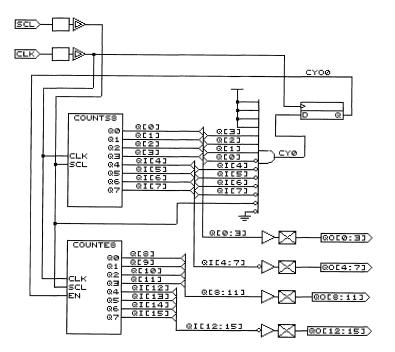

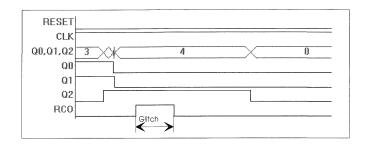

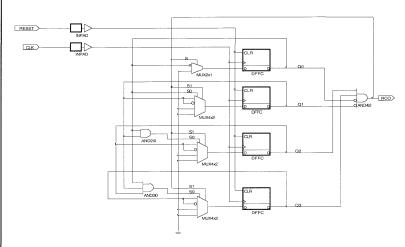

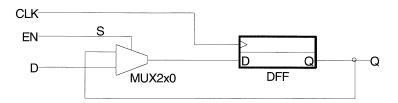

|        | QAN2 Counter Designs in the pASIC Devices            | 4-9               |

|        | QAN4 Fast Accumulators                               | 4-2               |

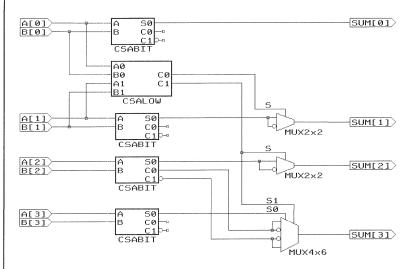

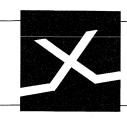

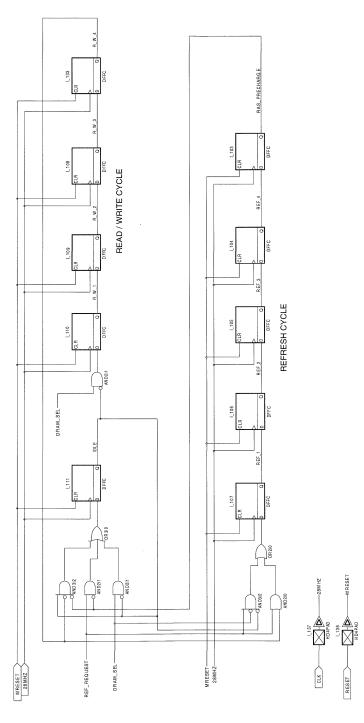

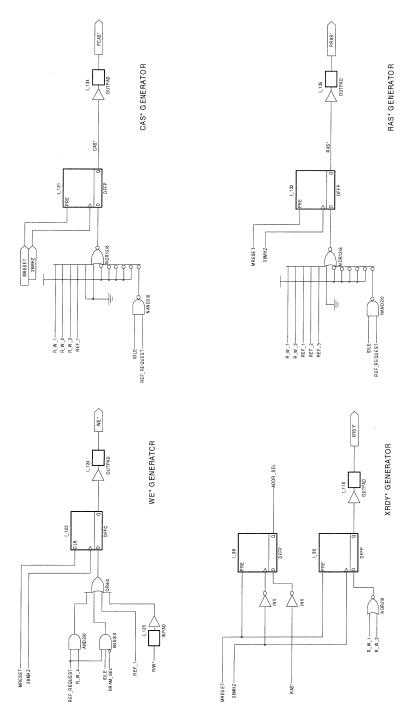

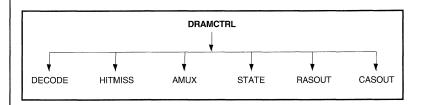

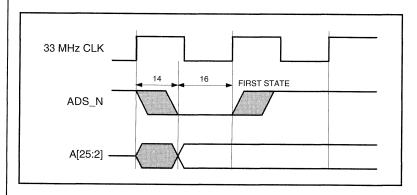

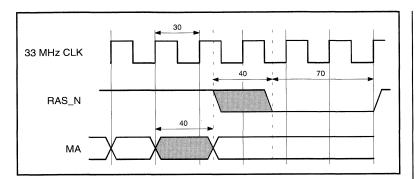

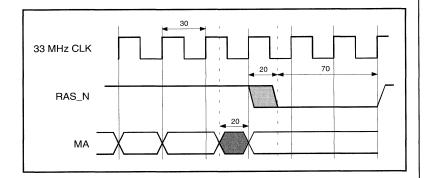

|        | QAN5 DRAM Controller for the TI TMS32C30             | 4-33              |

|        | QAN6 Page Mode DRAM Controller for 486DX             | 4-45              |

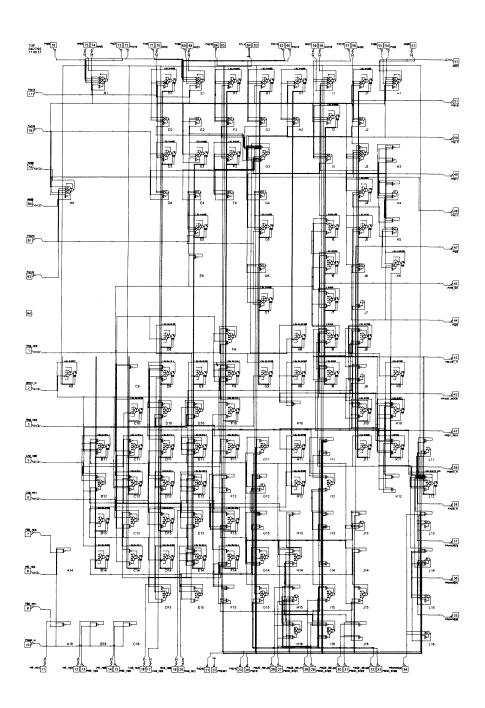

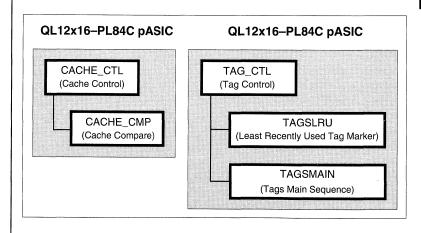

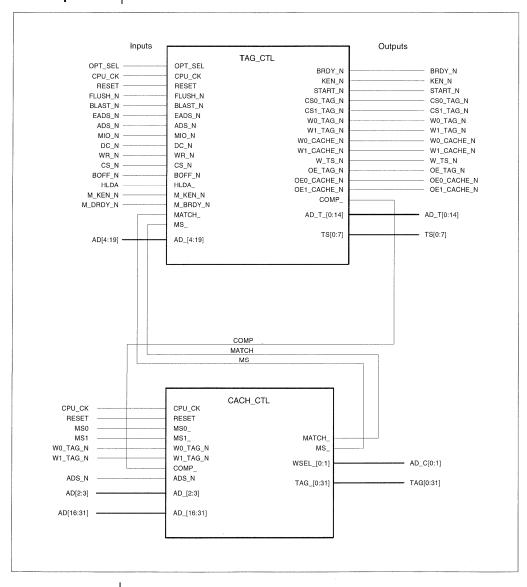

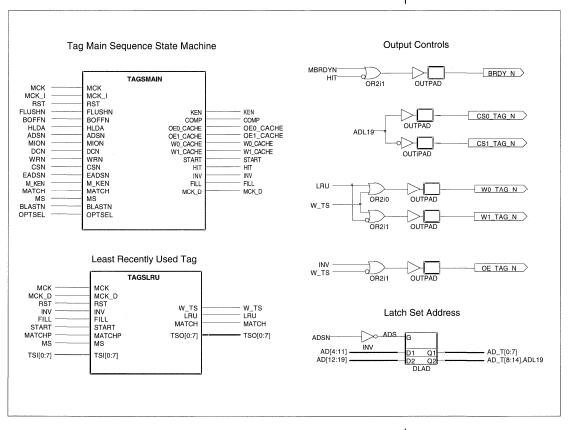

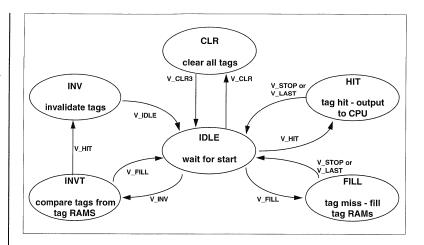

|        | QAN7 FPGA Cache Controller for the 486DX             |                   |

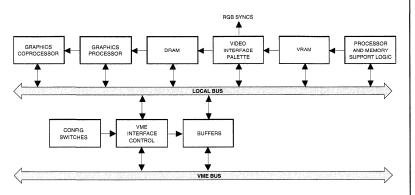

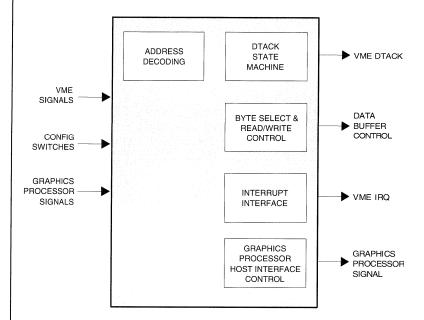

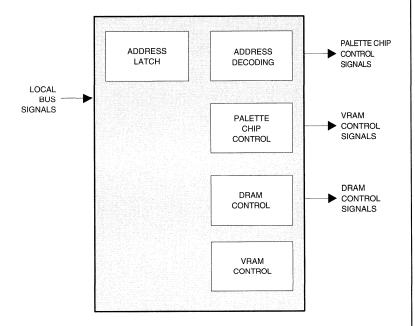

|        | QAN8 Video Support Logic and VME Interface           |                   |

|        | QAN9 Optimizing ASIC Architecture Designs            | 4-89              |

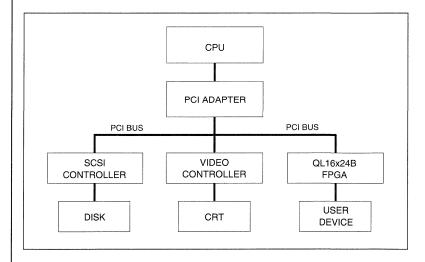

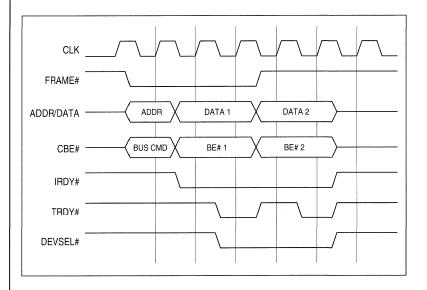

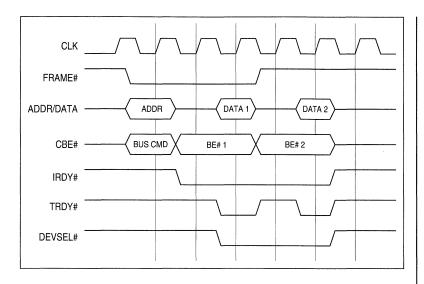

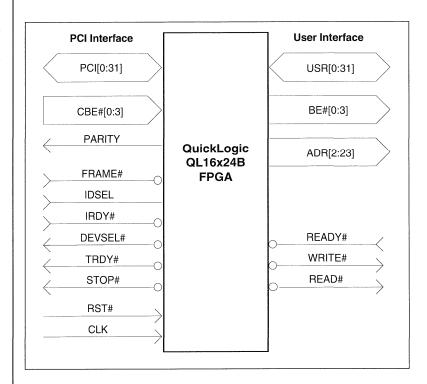

|        | QAN10 Peripheral Component Interconnect (PCI)        |                   |

|        | Using the QL16x24B FPGA                              |                   |

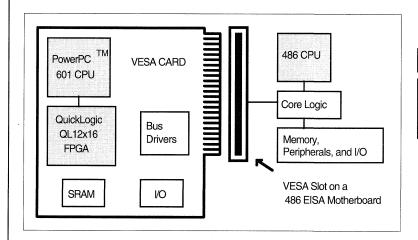

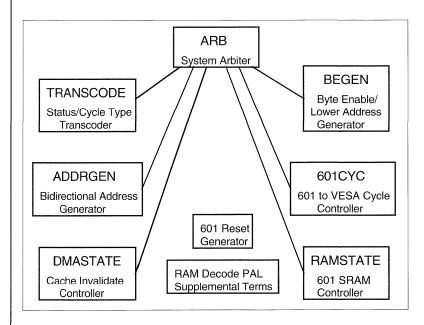

|        | QAN11 Power PC™ 601 CPU Interface to VESA Bus        |                   |

|        | QAN12 Designing with ABEL & Palasm                   | 4-130             |

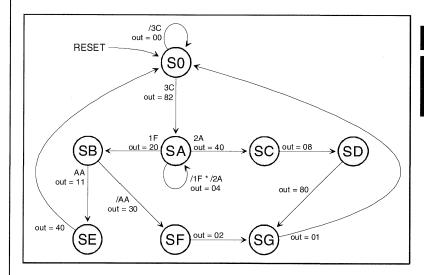

|        | QAN13 Implementing a One-Hot State Machine           | 4.40              |

|        | using QuickBoolean                                   | 4-13              |

|        | QAN14 Analyzing & Optimizing performance             | 4.4.4             |

|        | using QuickBoolean                                   | 4-14 <sup>-</sup> |

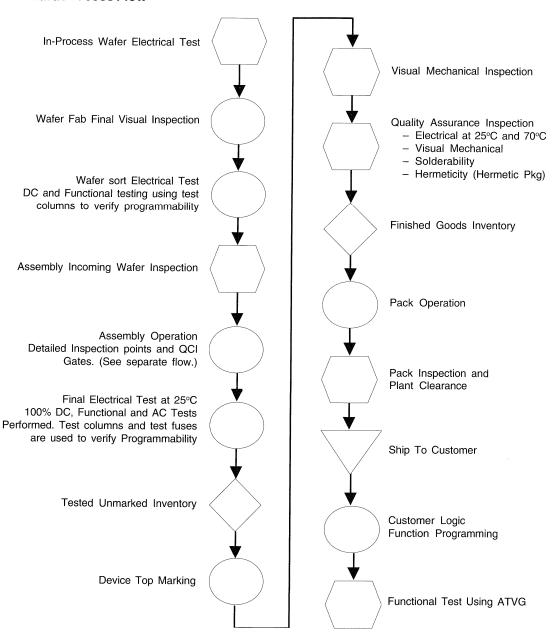

| Qualit | y, Reliability, and Packaging Information            |                   |

|        | Quality Program                                      | E :               |

|        | Reliability Report                                   |                   |

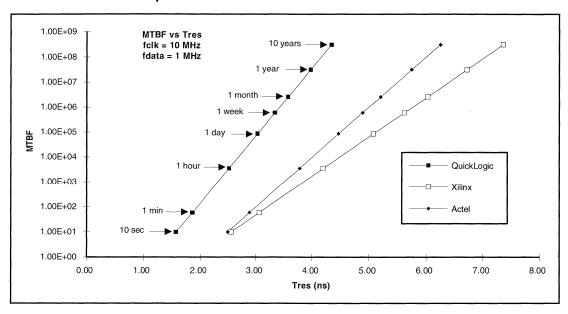

|        | Metastability Report for FPGAs                       |                   |

|        | Power vs Operating Frequency                         |                   |

|        | Thermal Management                                   |                   |

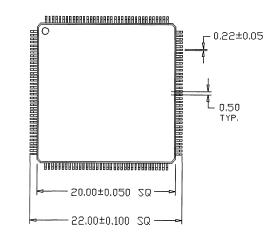

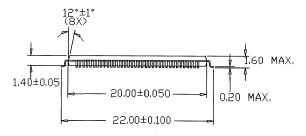

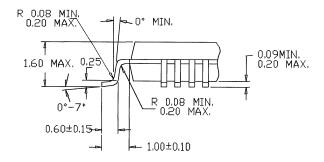

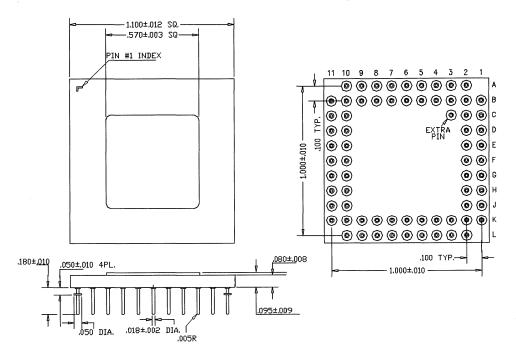

|        | Packaging Specifications                             |                   |

|        | Package Pin Bonding Cross Reference                  |                   |

|        | · ·                                                  |                   |

| Paper  | s and Article Reprints                               |                   |

|        | Papers and article reprints summary                  | 6- <sup>-</sup>   |

|        | IEDM paper                                           | 6-3               |

|        | IRPS paper                                           |                   |

|        | The PREP Benchmarks for FPGAs                        |                   |

|        | System Application Case Studies                      |                   |

|        | FPGA User Application Profiles                       |                   |

|        | Presentation Slides                                  | 6-37              |

|        |                                                      |                   |

| Sales  | Representatives and Distributors                     |                   |

|        | Sales Representatives/Distributors                   | 7- <sup>-</sup>   |

# **Quick Reference Product Guide**

# **PASIC DEVELOPMENT TOOLS**

| PART #          | PRODUCT NAME                     | DESCRIPTION                                                    |  |  |  |

|-----------------|----------------------------------|----------------------------------------------------------------|--|--|--|

| PC              |                                  |                                                                |  |  |  |

| QT-QWK-50-PC-A  | QuickWorks Toolkit               | Complete design kit for Windows-PC with programmer             |  |  |  |

| QT-QTL-50-PC-A  | QuickTools Toolkit               | Includes QS-SPDE-50-PC, QS-UTIL-50-PC and programmr.           |  |  |  |

| QT-SPDE-50-PC-A | SpDE Toolkit                     | Place & route with programmr. for users with third party tools |  |  |  |

| QS-QWK-50-PC    | QuickWorks Software              | Complete software package for Windows-PC                       |  |  |  |

| QS-QTL-50-PC    | QuickTools Software              | Includes QS-SPDE-50-PC & QS-UTIL-50-PC                         |  |  |  |

| QS-SPDE-50-PC   | SpDE Software                    | Place & route for users with third party tools                 |  |  |  |

| QS-UTIL-50-PC   | Software Utilities Package       | 3rd Party Simulation Interfaces, Logic Re-Optimizer            |  |  |  |

| QT-DP-50-PC-A   | Designer Programmer              | Up to eight programmers may be ganged off one computer         |  |  |  |

| QS-QWK-50-PC-EV | "Check-out Your Design" Eval Kit | Complete a full design! Includes 30 day license & support      |  |  |  |

| QS-VL-PC        | Viewlogic Technology Libraries   | For Workview Pro; Plus, supports Draw, Sim & Synthesis         |  |  |  |

| QS-INTG-PC      | Intergraph Technology Libraries  | For Intergraph design tools                                    |  |  |  |

|                 | S                                | UN                                                             |  |  |  |

| QS-QTL-50-SUN   | QuickTools Software              | Includes QS-SPDE-50-SUN & QS-UTIL-50-SUN                       |  |  |  |

| QS-SPDE-50-SUN  | SpDE Software                    | Place and route software for SUN SparcStation                  |  |  |  |

| QS-UTIL-50-SUN  | Software Utilities Package       | 3rd Party Simulation Interfaces, Logic Re-Optimizer            |  |  |  |

| QS-VL-SUN       | Viewlogic Technology Libraries   | Support for Powerview including ViewSynthesis                  |  |  |  |

| QS-SYN-SUN      | Synopsys Technology Libraries    | Support for Design Compiler with VHDL and Verilog              |  |  |  |

| QS-MEN-SUN      | Mentor Technology Libraries      | Support for Mentor Schematic Capture and Simulator             |  |  |  |

| QS-CNC-SUN      | Cadence Technology Libraries     | Support for Concept schematic package                          |  |  |  |

|                 |                                  | -IP                                                            |  |  |  |

| QS-QTL-50-HP    | QuickTools Software              | Includes QS-SPDE-50-HP & QS-UTIL-50-HP                         |  |  |  |

| QS-SPDE-50-HP   | SpDE Software                    | Place and route software for HP Workstation                    |  |  |  |

| QS-UTIL-50-HP   | Software Utilities Package       | 3rd Party Simulation Interfaces, Logic Re-Optimizer            |  |  |  |

| QS-MEN-HP       | Mentor Technology Libraries      | Support for Mentor Schematic Capture and Simulator             |  |  |  |

#### Notes:

- (1) All QT products include designer programmer unit, and (2) The "-A" suffix = 110V power, "-B" = 220V, "-C" = 240V(U.K).

- (2) -50 version numbers subject to change as products are upgraded.

- (3) Software listed above without a version number may have been revised. Please contact sales representative before ordering.

# QUICK REFERENCE PRODUCT GUIDE

# **FPGA DEVICES**

| PART#    | USABLE<br>GATES | LOGIC<br>CELLS | I/O PINS | HIGH-DRIVE/<br>CLOCK PINS | LOGIC<br>CELL<br>DELAY | CLOCK<br>SKEW         | PACKAGES |        |

|----------|-----------------|----------------|----------|---------------------------|------------------------|-----------------------|----------|--------|

|          |                 |                |          |                           |                        |                       |          | 44PLCC |

| 01.0540  | 1000            | 00             | F0       |                           |                        | 0.5                   | 68PLCC   |        |

| QL8x12   | 1000            | 96             | 56       | 8                         | < 2.0 nsec             | 2.0 nsec   < 0.5 nsec | 68PGA    |        |

|          |                 |                |          |                           |                        |                       | 100TQFP  |        |

|          |                 |                |          |                           |                        | nsec < 0.5 nsec       | 68PLCC   |        |

|          |                 |                |          |                           |                        |                       | 84PLCC   |        |

| QL12x16  | 2000            | 192            | 80       | 8                         | < 2.0 nsec             |                       | 84CPGA   |        |

|          |                 |                |          |                           |                        |                       | 100TQFP  |        |

|          |                 |                |          |                           |                        |                       | 100CQFP  |        |

|          |                 |                |          |                           |                        |                       | 84PLCC   |        |

|          |                 |                |          |                           |                        | 0.0                   | 100TQFP  |        |

| QL16x24  | 4000            | 384            | 114      | 8                         | .00 0000               |                       | 100CQFP  |        |

| QL16X24  | 4000            | 304            | 114      | 0                         |                        | 144TQFP               |          |        |

|          |                 |                |          |                           |                        |                       | 144CPGA  |        |

|          |                 |                |          |                           |                        |                       | 160CQFP  |        |

| 01.04*20 | 0000            | 700            | 100      | 0                         | . 0.0 ====             | 0.5                   | 144TQFP  |        |

| QL24x32  | 8000            | 768            | 180      | 8                         | < 2.0 nsec             | < 0.5 nsec            | 208PQFP  |        |

# **PROGRAMMING ADAPTERS**

| PART #    | DEVICES<br>SUPPORTED | DESCRIPTION                           |

|-----------|----------------------|---------------------------------------|

| QP-PL44   | QL8X12               | Adapts 44PLCC To Program/Tester Unit  |

| QP-PL68   | QL8X12,QL12x16       | Adapts 68PLCC To Program/Tester Unit  |

| QP-CG68   | QL8X12               | Adapts 68CPGA To Program/Tester Unit  |

| QP-CG84   | QL12X16              | Adapts 84CPGA To Program/Tester Unit  |

| QP-PF100  | QL8X12, QL12X16      | Adapts 100TQFP To Program/Tester Unit |

| QP-CF100  | QL12X16              | Adapts 100CQFP To Program/Tester Unit |

| QP-PL4084 | QL16X24              | Adapts 84PLCC To Program/Tester Unit  |

| QP-PF4100 | QL16X24              | Adapts 100TQFP To Program/Tester Unit |

| QP-CF4100 | QL16X24              | Adapts 100CQFP To Program/Tester Unit |

| QP-PF4144 | QL16X24              | Adapts 144TQFP To Program/Tester Unit |

| QP-CG4144 | QL16X24              | Adapts 144CPGA To Program/Tester Unit |

| QP-CF4160 | QL16X24              | Adapts 160CQFP To Program/Tester Unit |

| QP-PF8144 | QL24X32              | Adapts 144TQFP To Program/Tester Unit |

| QP-PQ8208 | QL24X32              | Adapts 208PQFP To Program/Tester Unit |

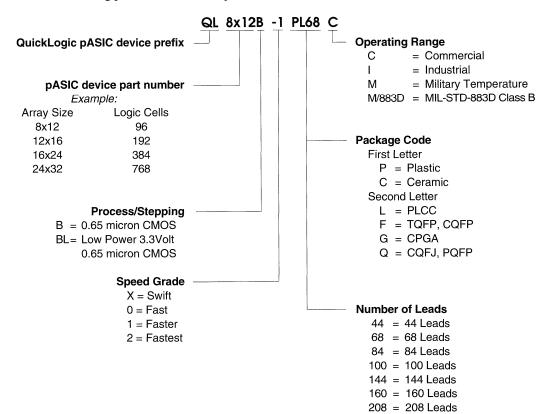

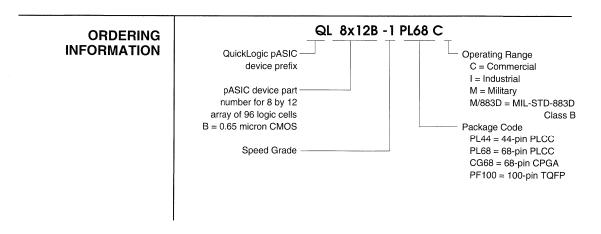

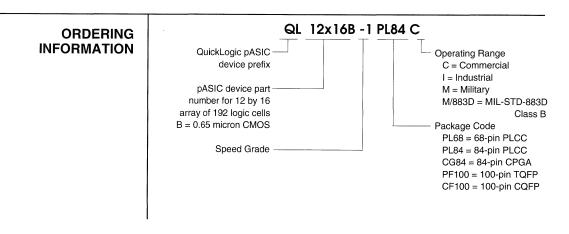

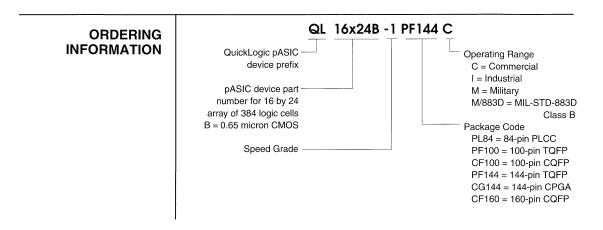

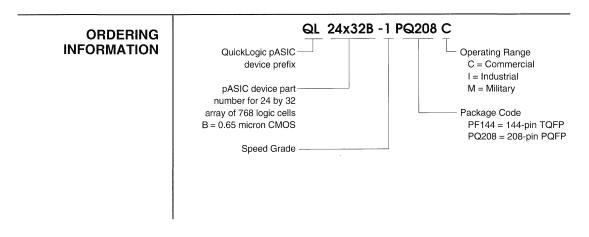

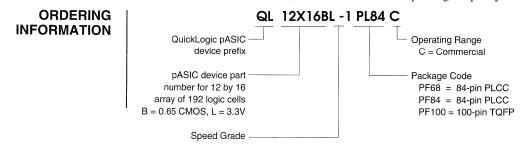

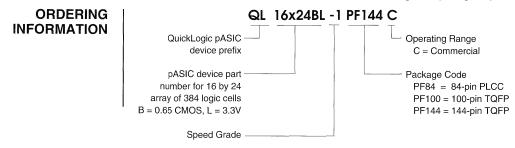

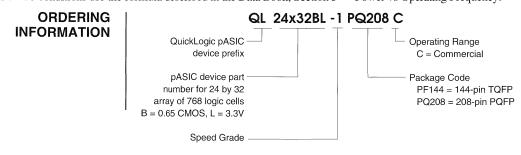

# **pASIC 1 FAMILY** Ordering Information

### **ORDERING INFORMATION**

pASIC device ordering part numbers are composed as follows:

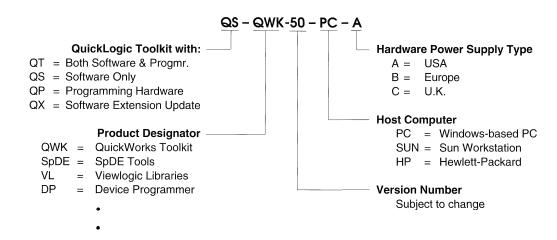

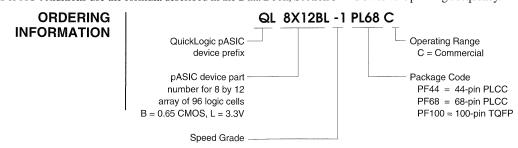

# **ORDERING INFORMATION**

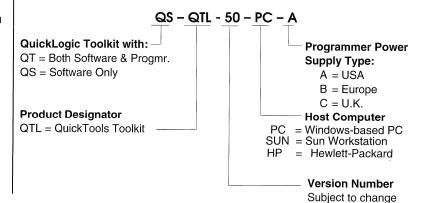

pASIC development tool ordering part numbers are composed as follows:

# Very-High-Speed FPGAs Through Technology, Architecture, and Tools

QuickLogic Corporation provides very-high-speed programmable ASIC solutions for designers of high-performance systems who must get their products to market quickly.

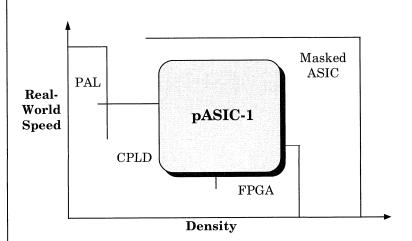

The company was founded by the engineers who invented the PAL device and PALASM software. By offering the ability to create high-speed custom logic circuits with standard off-the-shelf products, their invention revolutionized the world of logic design. First-generation FPGAs extended these benefits to higher levels of density, but at much lower speeds. QuickLogic was formed to create a single solution combining the fast speed of PAL devices with the high density, low power and logic flexibility of FPGAs.

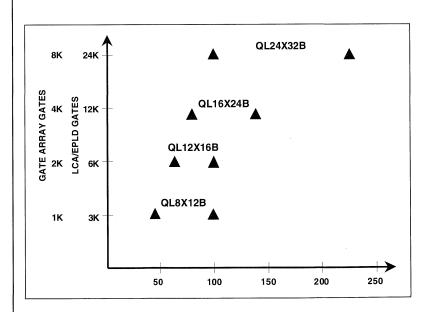

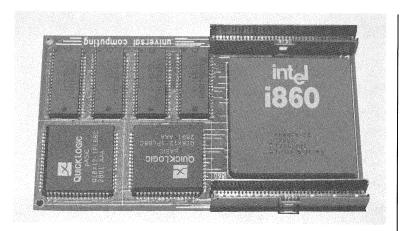

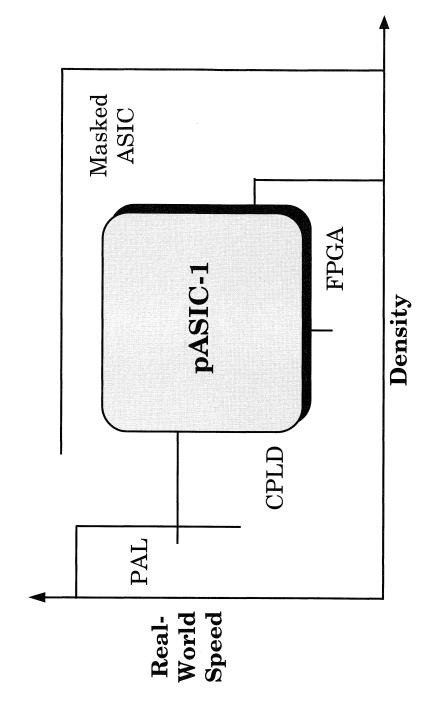

FIGURE 1 Comparative Speed/Density Chart

...FPGAs operating two to three times faster

QuickLogic FPGAs operate at two to three times the usable system speed of first-generation devices.

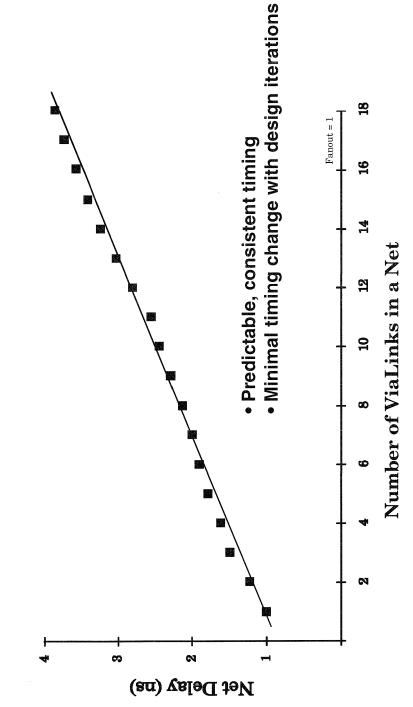

To achieve these goals, QuickLogic has created a CMOS antifuse technology, called the ViaLink<sup>TM</sup> element, which couples small size with high speed. It results in FPGAs operating two to three times faster than other technologies using the same process lithography. The small size also provides a technology migration path to 50,000 gates and beyond.

# X

## **VERY-HIGH-SPEED FPGAs**

...can be used in applications with 33, 66 and 80 MHz microprocessors QuickLogic's new *Wild*Cat series of devices in the pASIC 1<sup>TM</sup> Family of Very-High-Speed CMOS FPGAs, delivers new levels of speed and density in an easy-to-use product. High-density programmable devices can now be used in applications with 33, 66 and 80 MHz microprocessors and in designs with useful internal logic functions operating at over 150 MHz.

QuickLogic engineers achieve industry-leading performance by addressing the design task through the three aspects of Technology, Architecture, and Tools. In each area they combine a variety of techniques to yield the optimum solution.

### **Speed Through Technology**

- ViaLink direct metal-to-metal antifuse

- Speed-critical links less than 50 ohms

- Standard high-speed 0.65 micron CMOS logic process

These features yield both the smallest physical programming element size and *fastest interconnect* speed of all programmable technologies.

### **Speed Through Architecture**

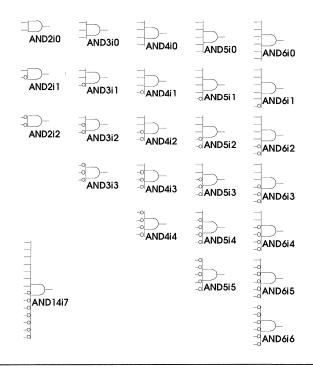

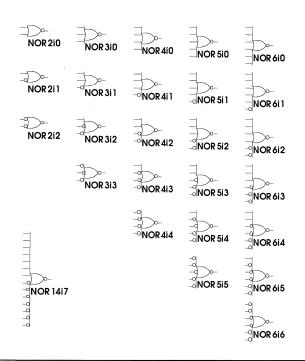

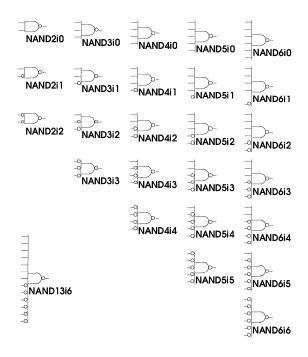

- Up to 14-input wide gates

- Highly tuned, dedicated register in every logic cell

- Plentiful regular and orthogonal interconnect wiring resources

These features provide an architecture optimized for a wide range of high-speed control, data path and general-purpose logic integration applications.

#### **Speed Through Tools**

- Architecture-optimized place and route tools

- Precise timing simulation using actual wire lengths, fanout, and loading

- Rapid design iterations permit design optimization

Users achieve high speed and fast design implementation through 100% automatic place and route tools even on functions using up to 100% of the available logic cells.

# ...100% automatic place and route

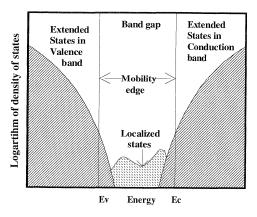

At the heart of every programmable device is an electronic switch for user configuration of on-chip logic functions. It may be an active device, such as an EPROM cell or an SRAM bit. Or a passive fuse or an antifuse element.

Two basic electrical characteristics limit the maximum useful operating speed which can be achieved with each approach.

- The capacitance, C, of the programmable element in the OFF (OPEN) state. This determines the capacitive loading effect of unprogrammed elements on metal interconnect wires.

- The resistance, R, of the programmable element in the ON (CLOSED) state. This determines the series resistance of the programmed element when interconnecting wires and logic functions.

The technology with the lowest values of R and C delivers the fastest raw speed to the circuit designer.

Other CMOS programmable ASIC devices using EPROM and SRAM programming elements typically have high resistance values, above 1000 ohms, plus large physical size. Dielectric antifuses improve on both these factors but still cannot yield the performance demanded by today's systems.

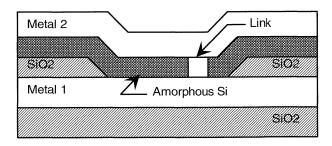

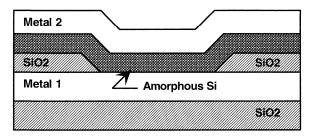

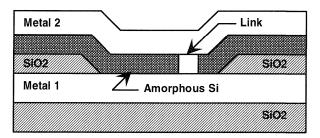

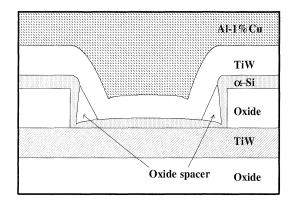

QuickLogic created the ViaLink antifuse to provide a low-resistance, low-capacitance programmable connection directly from one metal layer to another. The ViaLink element is formed by depositing a very high resistance layer of programmable silicon into a via between the two metal layers of a standard high-volume CMOS gate array process.

The ViaLink element provides a direct metal-to-metal connection.

## SPEED THROUGH TECHNOLOGY

ViaLink Antifuses

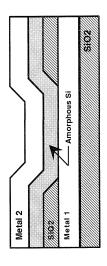

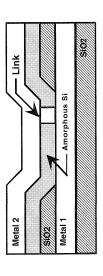

FIGURE 2 ViaLink Cross Section

# X

### **VERY-HIGH-SPEED FPGAs**

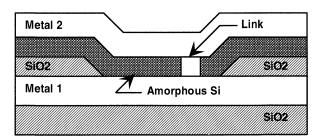

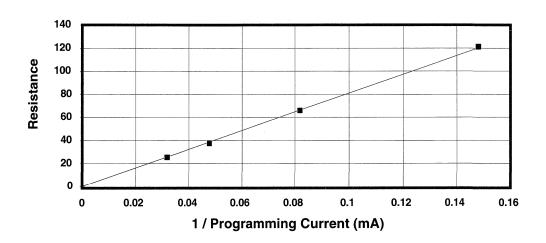

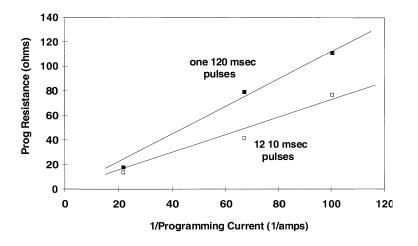

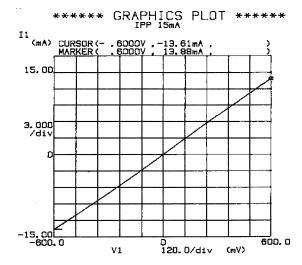

A programming voltage is applied to selected vias in an algorithm of pulses. This creates a direct metal-to-metal link by permanently converting the silicon to a low resistance state. Typical resistance is less than 50 ohms.

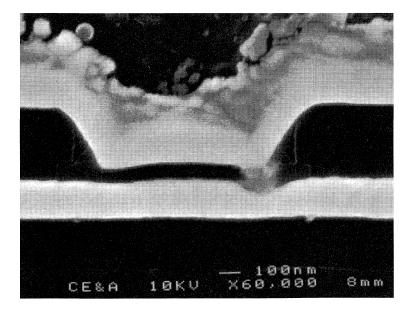

In a 0.65 micron process, the size of a ViaLink via is approximately one micron square, orders of magnitude smaller than active elements. This, coupled with the high dielectric constant of the via material, ensures that unprogrammed ViaLink devices exhibit low capacitive loading (less than 1fF). As the size of the programmed link is physically much smaller than the via, the technology can be scaled below 0.5 microns for future very-high-density applications.

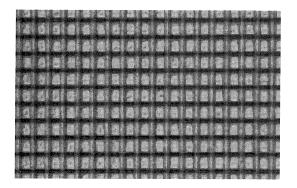

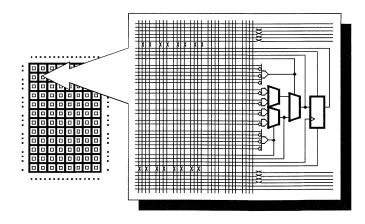

FIGURE 3

Photomicrograph

of an Array of

ViaLink Elements

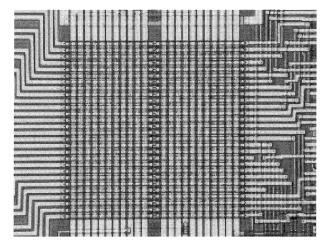

A ViaLink antifuse is located at the intersection of every horizontal and vertical wire. Array density is limited by the process lithography, not by the programmable element size.

### **EPLD AND FPGA TECHNOLOGY COMPARISONS**

| Programmable Element      | SRAM       | E/EEPROM  | Dielectric<br>Antifuse | ViaLink<br>Antifuse |

|---------------------------|------------|-----------|------------------------|---------------------|

| Typical ON Resistance R   | ~1000 ohm  | ~1000 ohm | ~500 ohm               | ~50 ohm             |

| Typical OFF Capacitance C | ~50 fF     | ~15 fF    | ~5 fF                  | ~1 fF               |

| Physical Size             | Very Large | Large     | Medium                 | Small               |

The ViaLink element delivers the lowest ON resistance, lowest OFF capacitance and smallest physical size of any programmable technology. These characteristics open up a new spectrum of high-speed, high-density applications to programmable devices.

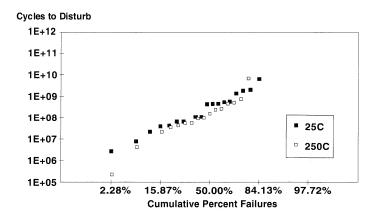

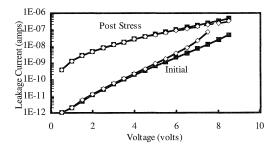

ViaLink elements have been subjected to accelerated stress testing in both programmed and unprogrammed states. Test results indicate that the ViaLink element has no measurable impact on the reliability of the underlying CMOS process. Product reliability levels in the system environment compare favorably with gate arrays and other FPGAs.

A wealth of interconnect resources, a performance-oriented logic cell, and optimized I/O circuitry maximize the fundamental speed advantage of the ViaLink technology.

Many FPGAs employ a variety of wiring types to limit the number of highresistance connections in a net. For example, signals can be routed through a variety of short lines, long lines, switch boxes and other structures. These irregular routing resources cause unpredictable delay behavior and limit logic utilization.

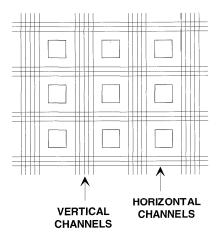

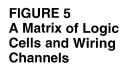

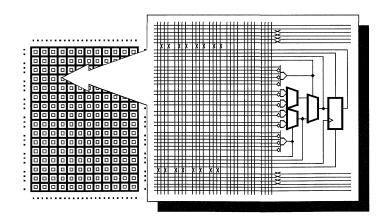

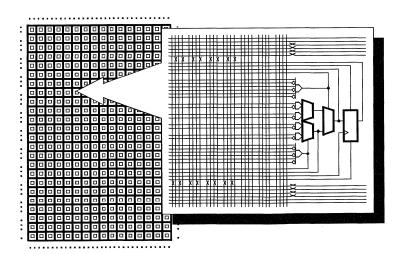

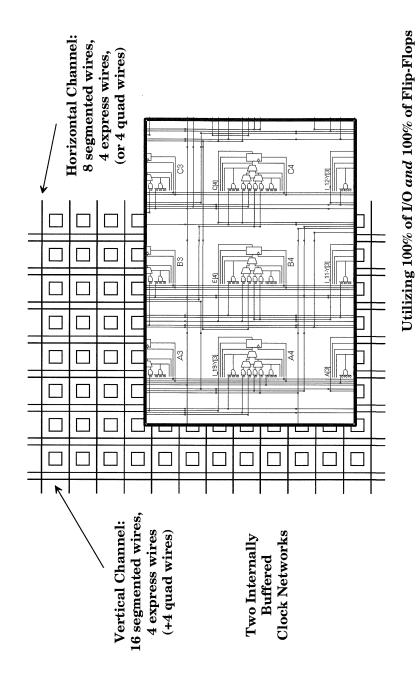

The low impedance of the ViaLink antifuse allows a regular and orthogonal architecture. The pASIC structure features a matrix of logic cells interconnected by vertical and horizontal routing channels. A ViaLink element located at every wire intersection allows direct, metal-to-metal links between signal lines.

A matrix of speed-optimized logic cells is set in a grid of vertical and horizontal wiring channels which can be selectively connected with metal-to-metal links. ViaLink Reliability

SPEED THROUGH ARCHITECTURE

Fast, Yet Regular Routing

FIGURE 4 pASIC Architecture

1-9

According to users (*Computer Design*, 12/91, pg. 78), QuickLogic FPGAs are the closest to masked gate arrays both in predictability and in absolute levels of performance.

- Delays are "predictable no matter what the layout is."

- "Wire delays are shorter than logic delays."

- As net lengths increase, delays increase proportionally.

- Small design changes result only in small changes in speed.

All these characteristics allow rapid iteration towards the fastest possible solution.

# High-Speed Logic Cell

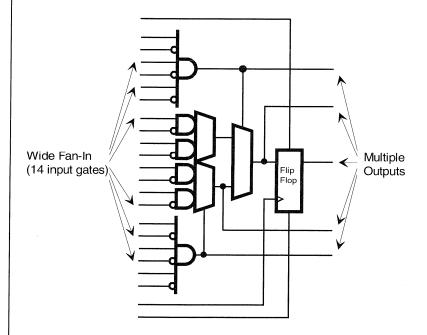

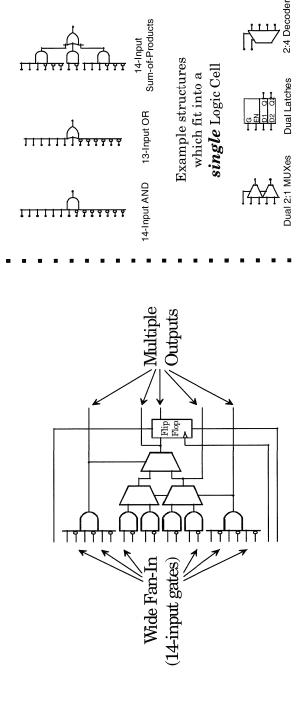

The pASIC logic cell is optimized for high-speed applications. Gates up to 14 inputs wide, multiplexers, decoders and sum-of-products functions can be implemented in a single cell delay with worst case commercial  $t_{\rm PD}$  of under 2.5 ns. Many logic functions therefore incur just half the propagation delay of traditional, narrow fan-in, FPGA logic cell structures.

# FIGURE 5 pASIC 1 Logic Cell

...24-bit loadable counters operate at over 125 MHz

The wide fan-in and multiple outputs of the pASIC logic cell permit high-speed logic functions and efficient use of resources.

Each cell includes a dedicated, highly-tuned register element. Simple Johnson counters run at 214 MHz. 24-bit loadable counters, capable of doing useful work, require one logic cell delay and operate at over 150 MHz.

Fast sum-of-product state machines require just two cell delays. Complex arithmetic functions using up to three levels of logic run faster than 90 MHz.

16-bit Johnson Counter 214 MHz 1 cell level Datapath Multiplexer 206 MHz 1 cell level 24-bit Loadable Counter 1 cell level 154 MHz Sum-Of-Products State Machine 106 MHz 2 cell levels 8-bit Adder 3 cell levels 92 MHz Typical examples of speed versus logic function complexity.

FIGURE 6 Real World Operating Speeds of 50 to 125 MHz

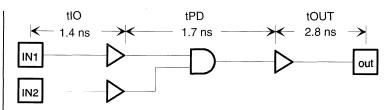

These impressive on-chip specs are matched by fast I/O performance. Worst case commercial input pad to output pad delay through a 14-input AND gate, or a 4-input MUX, for example, is less than 10 ns.

Fast I/O circuits allow logic functions in separate packages to operate together at over 75 MHz. This speed is achieved while preserving low output switching noise levels. Switching of up to 48 outputs simultaneously has been demonstrated with less than 1 volt of ground bounce.

Fast I/O

# FIGURE 7 Fast I/O Pads

QL16x24B Nominal I/O Delays

Input Delay + Combinatorial Delay + Output Delay = 5.9 ns

Input Delay + Reg Setup + Clock to Output + Output Delay = 7.3 ns

# SPEED THROUGH TOOLS

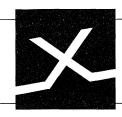

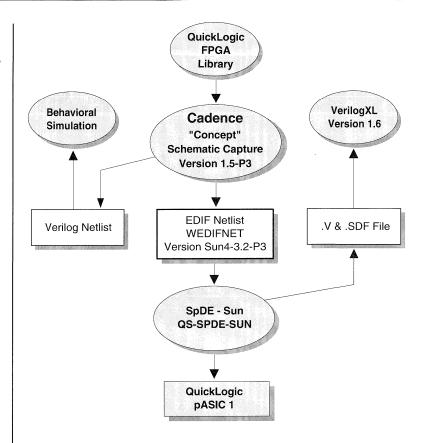

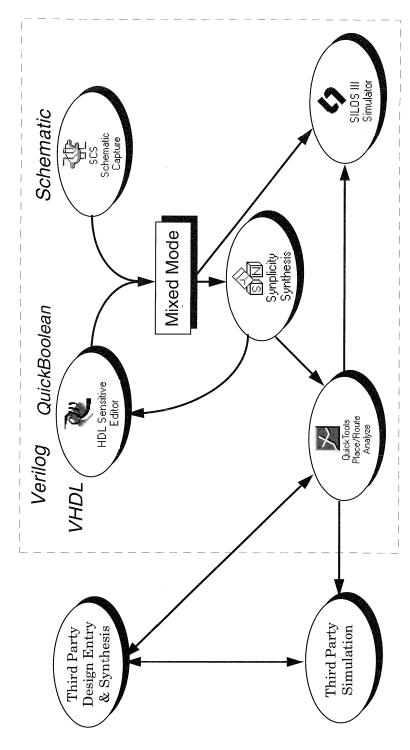

Fast device operation and rapid design execution is achieved by combining the best third-party CAE tools with device-specific place and route and delay modeling software.

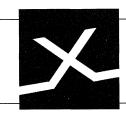

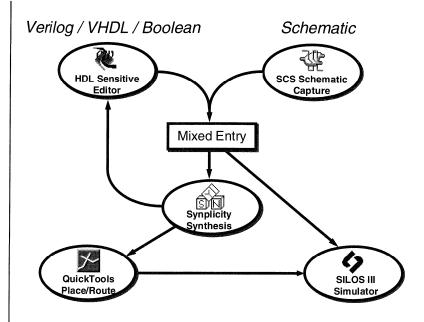

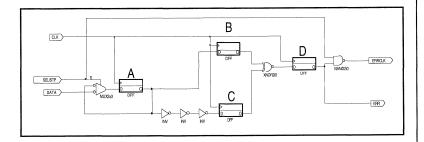

# FIGURE 8 The pASIC Toolkit

QuickLogic tools communicate with third-party software through an object-oriented design database.

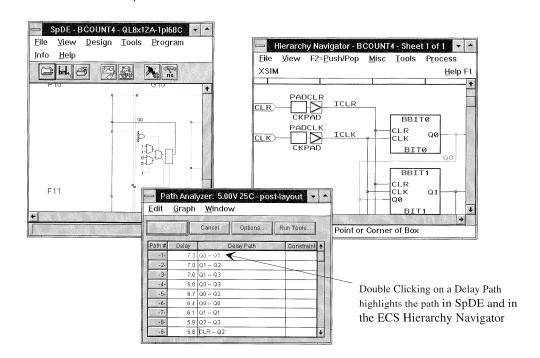

Designs can be created using general-purpose schematic, language entry and simulation packages on PC, Sun and HP workstation platforms. These tools interface to the QuickLogic Seamless pASIC Design Environment (SpDE — pronounced "Speedy") for optimization place and route, delay modeling, and other tasks best served by architecture specific code.

VHDL, Verilog, state machine, and Boolean (ABEL, CUPL, MINC, PALASM, etc.) language entry are available through several tool and synthesis package vendors (Data I/O, Viewlogic, Synopsys, Exemplar, Cadence, Intergraph).

A low-cost, fully integrated design solution operating under Microsoft Windows on a PC is all that is needed to complete a design. The Quick Works tookit includes Verilog/VHDL Synthesis, Context Sensitive HDL Editing, Color Coded HDL Template Expansion, Mixed-Mode Design Entry, Enhanced Schematic Capture, Comprehensive Verilog Simulation plus QuickLogic's SpDE software. The package can also include a device programmer.

The regular gate array-like architecture, combined with abundant routing resources, enables 100% automatic placement and routing with high utilization. Users report completing designs using 100% of the logic cells, even with a large number of fixed pin locations.

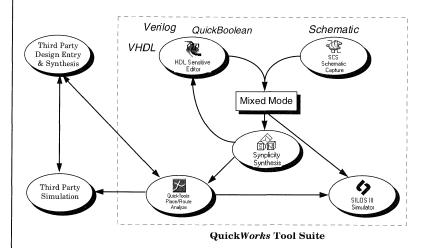

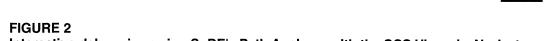

A physical viewer shows how the automatic tools fit logic functions into the silicon resources, right down to specific routing wires utilized.

A path analyzer provides timing for selected interconnect nets in the device without having to run the simulator. It also allows entry of specific timing requirements, by path, for SpDE to use in timing-driven placement to meet your timing requirements.

Cross probing between applications allows for easy analysis of designs and fast debugging of problems. Click on a net in the schematic and it is instantly highlighted in the physical layout. Or vice versa. Similar interactive links exist to the simulator, and path analyzer.

Design Entry: Third Party & QL Integrated

Quick Works

Optimized Place and Route

# FIGURE 9 Windows Screen Shot

## **Precise Timing**

Asymptotic Waveform Evaluation, AWE, techniques generate precise timing data, using actual circuit wire lengths, fanout and loading. This enhances speed by providing accurate delay models for back annotation into the simulator. It also identifies the most heavily loaded nets for selective programming to less than 50 ohms.

# Test Vectors and Programming

Scan path circuitry built into the pASIC flip-flops allows automatic generation of test vectors for post-programming functional testing.

Programmers attach to the PC via the RS-232 port. No special-purpose programming cards occupy valuable expansion slots.

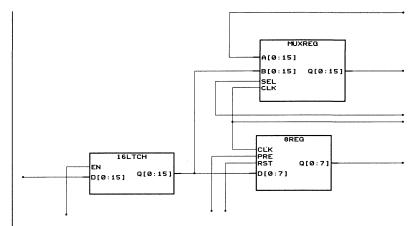

The pASIC 1 Family serves general-purpose, high-speed logic integration tasks in arithmetic, control, data path and RISC and CISC microprocessor support applications. Four basic devices cover a broad range of speed, package, density, and I/O options.

Device part numbers describe the organization of logic cells. For example, the QL8x12B features 96 logic cells in an eight by twelve matrix. A fully utilized QL8x12B accommodates 800 to 1200 gates, for an average of ten gates per cell. QuickLogic describes this as a 1000 usable-gate FPGA. It is equivalent in capacity to many, so called "3000 to 4000 gate" EPLD and LCA devices.

As each logic cell contains a dedicated register function plus combinatorial logic sufficient to create two latches, the QL8x12B can contain up to 288 storage elements.

| Part<br>Number | Logic<br>Cells | Storage<br>Elements | Max I/O<br>Cells | Dedicated Inputs | Package<br>Pins      | Usable<br>Gates | CPLD/LCA<br>Gates |

|----------------|----------------|---------------------|------------------|------------------|----------------------|-----------------|-------------------|

| QL8x12B        | 96             | 288                 | 56               | 8                | 44, 68, 100          | 1000            | 3000              |

| QL12x16B       | 192            | 576                 | 80               | 8                | 68, 84, 100          | 2000            | 6000              |

| QL16x24B       | 384            | 1152                | 114              | 8                | 84, 100,<br>144, 160 | 4000            | 12000             |

| QL24X32B       | 768            | 2304                | 172              | 8                | 144, 208             | 8000            | 24000             |

# PASIC 1 FAMILY PRODUCTS

**Family Features**

# X

## **VERY-HIGH-SPEED FPGAs**

#### **Product Features**

PLCC, TQFP, CPGA, CQFP and other package styles are available. Multiple speed selections for each device allow the user to trade-off performance and cost.

For worst-case commercial:

- Input buffer plus logic cell plus output buffer delay of under 10 ns.

- Multiple-chip operating frequencies over 75 MHz.

- Logic function delays, up to two levels deep, in under 2.5 ns.

- Useful counter speeds up to 125 MHz.

- Low output switching noise. Less than 1 volt of ground bounce with 48 outputs switching simultaneously.

- Worst-case clock skew of less than 1 ns.

- Input hysteresis provides high reliability in noisy operating environments.

- Low CMOS power consumption: typically 2 mA standby current.

# Future pASIC Families

Future pASIC products will use the small size of the ViaLink element to offer FPGA families with densities and I/O counts comparable to today's masked gate arrays. ViaLink technology will also be used to extend the flexibility and ease of use of user-configurable logic to new programmable ASIC architectures.

# pASIC 1 FAMILY ViaLink Technology Very-High-Speed CMOS FPGAs

# FAMILY HIGHLIGHTS

- Very High Speed ViaLink metal-to-metal, programmable-via antifuse technology ensures useful internal logic function speeds at over 100 MHz, and logic cell delays of under 2 ns.

- High Usable Density Up to 8,000 "gate array" gates, equivalent to 24,000 EPLD or LCA Gates.

- Low Power/ 3.3 Volt Supply— Stand-by current typically 2 mAwith 5.0 Volt supply and less than 1 mA with 3.3 Volt supply.

- Flexible FPGA Architecture The pASIC 1 logic cell supports efficient, high-speed arithmetic, counter, data path, state machine and random logic applications with up to 14-input wide gates.

- Low-Cost, Easy-to-Use Design Tools Designs entered and simulated using third-party CAE tools. Fast, fully automatic place and route on PC and workstation platforms.

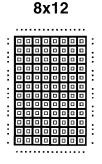

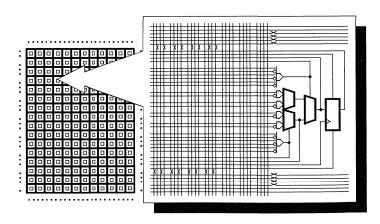

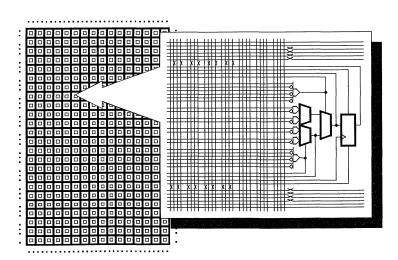

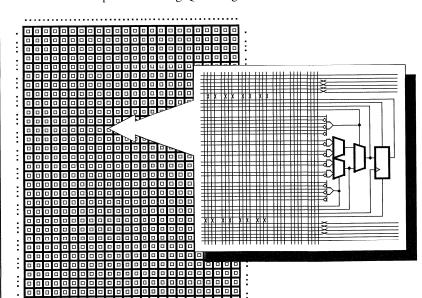

# FIGURE 1 pASIC 1 Family

## FAMILY SUMMARY

The pASIC 1 Family of very-high-speed CMOS user-programmable ASIC (pASIC) devices is based on the first FPGA technology to combine high speed, high density and low power in a single architecture.

All pASIC 1 Family devices are based on an array of highly flexible logic cells which have been optimized for efficient implementation of high-speed arithmetic, counter, data path, state machine, random and glue logic functions. Logic cells are configured and interconnected by rows and columns of routing metal and ViaLink metal-to-metal programmable-via interconnect elements.

ViaLink technology provides a nonvolatile, permanently programmed custom logic function capable of operating at counter speeds of over 150 MHz. Internal logic cell nominal worst case delays are under 2 ns and total input to output combinatorial logic delays are under 8 ns. This permits high-density programmable devices to be used with today's fastest CISC and RISC microprocessors, while consuming a fraction of the power and board area of PAL, GAL and discrete logic solutions.

pASIC 1 Family devices range in density from 1000 "gate array" gates (3,000 EPLD/LCA gates) in a 44-pin package, to 8,000 (24,000) gates in high-pin-count packages. All devices share a common architecture and CAE design software to allow easy transfer of designs from one product to another. The small size of the ViaLink programming element ensures a technology migration path to devices of 20,000 gates and above.

Designs are entered into the pASIC 1 Family of devices on PC or workstation platforms using third-party, general-purpose design-entry and simulation CAE packages, together with QuickLogic device-specific place and route and programming software, called SpDE tools. Sufficient on-chip routing channels are provided to allow fully automatic place and route of designs using up to 100% of the available logic cells.

All the necessary hardware and software, required to complete a design, from entering a schematic to programming a device are included in pASIC Toolkits available from QuickLogic. The Quick*Works* Toolkit includes Verilog®/VHDL Synthesis, Context Sensitive HDL Editing, Color Coded HDL Template Expansion, Mixed-Mode Design Entry, Enhanced Schematic Capture, Comprehensive Verilog Simulation plus QuickLogic's SpDE software. All applications run on the PC under the Microsoft Windows 3.1 & NT graphical user interface to ensure a highly productive and easy-to-use design environment. An open interface (QDIF) allows many other third-party tools (Exemplar, Viewlogic, etc.) to be used with QuickLogic software on both PC and workstation platforms.

Programmable devices implement customer-defined logic functions by interconnecting user-configurable logic cells through a variety of semiconductor switching elements. The maximum speed of operation is determined by the effective impedance of the switch in both programmed, ON, and unprogrammed, OFF, states.

In pASIC 1 devices the switch is called a ViaLink element. The ViaLink element is an antifuse formed in a via between the two layers of metal of a standard CMOS gate array process. The direct metal-to-metal link created as a result of programming achieves a connection with resistance values below 50 ohms. This is less than 5 percent of the resistance of an EPROM or SRAM switch and 10 percent of that of a dielectric antifuse. The capacitance of an unprogrammed ViaLink site is also lower than these alternative approaches. The resulting low RC time constant provides speeds two to three times faster than older generation technologies.

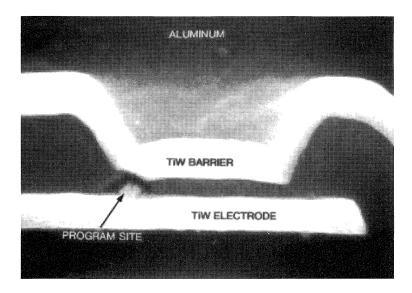

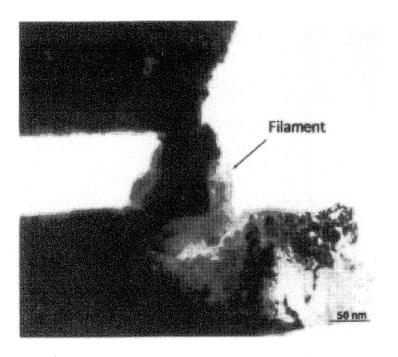

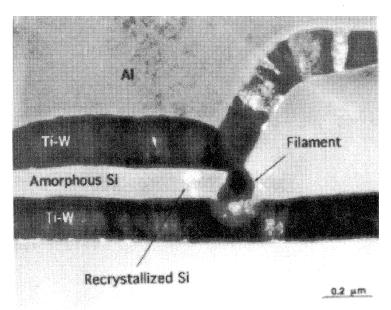

Figure 2a shows an unprogrammed ViaLink site. In a custom metal masked ASIC, such as a gate array, the top and bottom layers of metal make direct contact through the via. In a ViaLink programmable ASIC device the two layers of metal are initially separated by an insulating silicon layer with resistance in excess of 1 gigaohm.

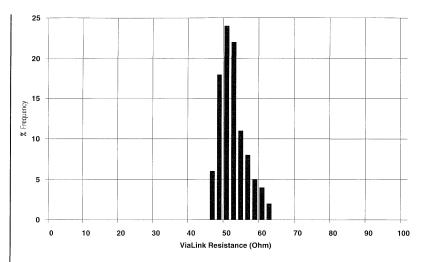

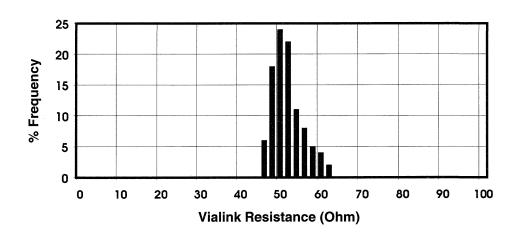

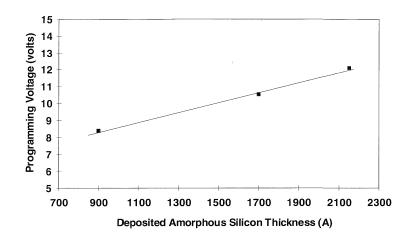

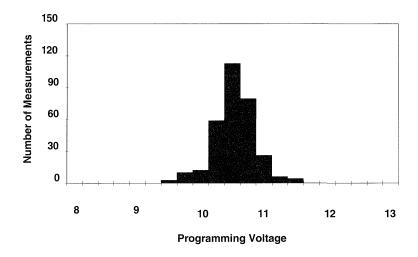

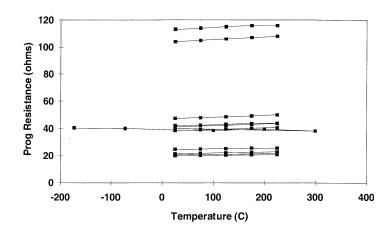

A programming voltage pulse applied across the via forms a bidirectional conductive link connecting the top and bottom metal layers, Figure 2b. The tight distribution of link resistance is shown in Figure 3.

VIALINK PROGRAMMING ELEMENT

FIGURE 2a Unprogrammed ViaLink Element

FIGURE 2b Programmed ViaLink Element

# FIGURE 3 Distribution of Programmed Link Resistance

# STANDARD CMOS PROCESS

QuickLogic pASIC 1 devices are the first FPGA devices to be fabricated on a conventional high-volume CMOS gate array process. The base technology is a 0.65 micron, n-well CMOS technology with a single polysilicon layer and two layers of metal interconnect. The only deviation from the standard process flow occurs when the ViaLink module is inserted between the metal deposition steps.

# FIGURE 4 An Array of ViaLink Elements

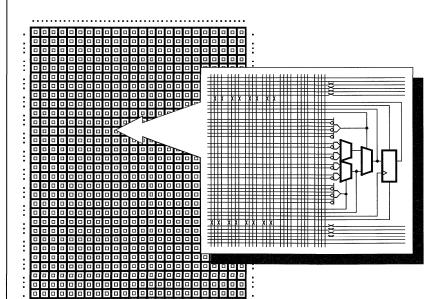

As the size of a ViaLink via is identical to that of a standard metal interconnect via, programmable elements can be packed very densely. The microphotograph of Figure 4 shows an array of ViaLink elements. The density is limited only by the minimum dimensions of the metal-line to metal-line pitch. Migration of processes to submicron geometries will allow the development of pASIC 1 devices with tens of thousands of usable gates.

# X

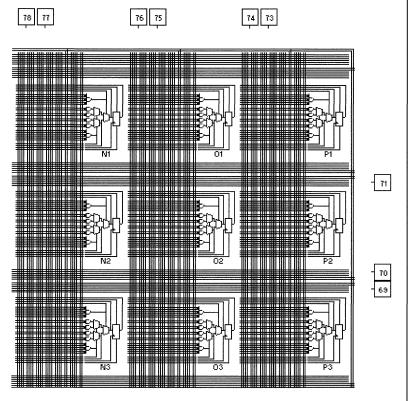

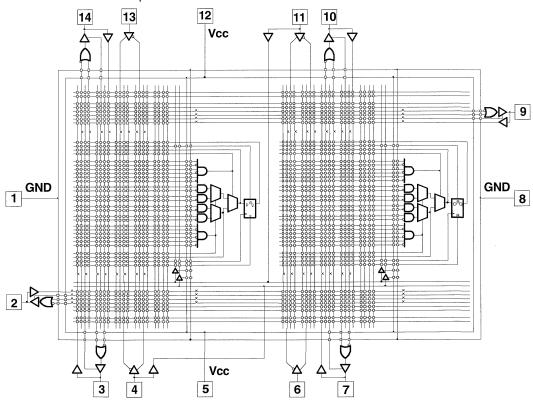

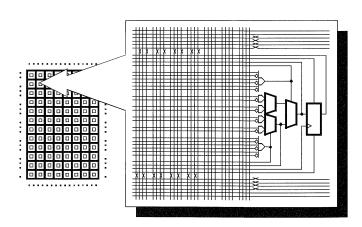

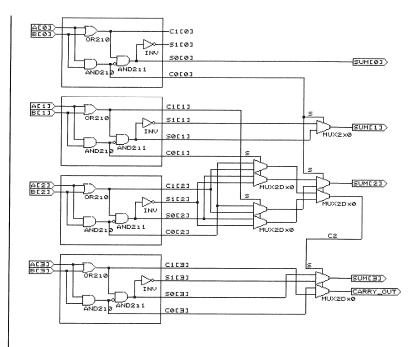

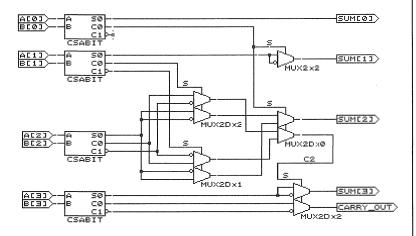

The pASIC 1 device architecture consists of an array of user-configurable logic building blocks, called logic cells, set in a grid of metal wiring channels similar to those of a gate array. Figure 5 shows a section of a pASIC 1 device containing internal logic cells, input/output cells and dual-layer vertical and horizontal metal routing channels. Through ViaLink elements located at the wire intersections, the output of any cell may be programmed to connect to the input of any other cell.

# PASIC FAMILY ARCHITECTURE

This regular and orthogonal interconnect makes the pASIC 1 architecture similar in structure and performance to a metal masked gate array. It also makes system operating speed far less sensitive to partitioning and placement decisions, as minor revisions to a logic design result only in small changes in performance.

Adequate wiring resources permit 100% automatic placement and routing of designs using up to 100% of the logic cells. This has been demonstrated on designs that include a high percentage of fixed pin placements.

#### **ORGANIZATION**

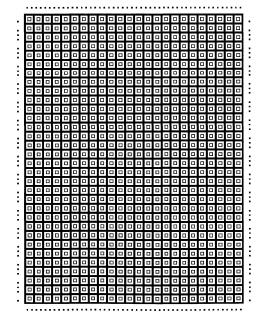

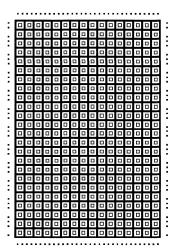

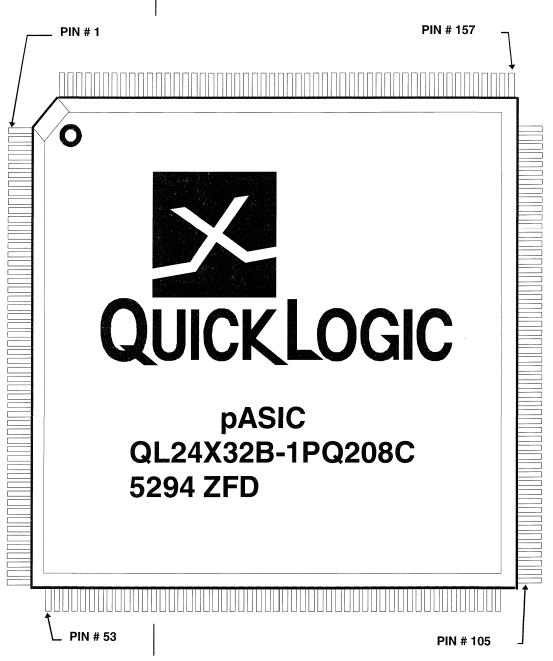

The pASIC 1 Family of very-high-speed FPGAs contains devices covering a wide spectrum of I/O and density requirements. The four members range from 1,000 gates in a 44-lead package to 8000 gates in a 208-lead package and are shown in Figure 6.

Device part numbers are derived from the organization of internal logic cells. For example, in Figure 6, the QL8x12B contains 96 logic cells in an 8-by-12 matrix. The single lines between logic cells represent channels containing up to twenty-two wires. Each of the internal logic cells has the logic capacity of up to 30 "gate array gates." As a typical application will use 10 to 12 gates from each logic cell, the QL8x12B is described as a 1000-usable-gate device. Based on the "available gate" gate counting approach of some programmable logic vendors, it would be called a 3000-gate part. The QL8x12B is available in a 68-lead package with 56 bidirectional I/O pins and 8 dedicated input/high drive clock pins and a 44-lead package with 32 I/O pins.

The key features of these four pASIC 1 devices are as follows:

| Device<br>Cells | Logic<br>Cells | Max I/O<br>Inputs | Dedicated<br>Pins | Package<br>Pins | Usable<br>Gates | EPLD/LCA<br>Gates |

|-----------------|----------------|-------------------|-------------------|-----------------|-----------------|-------------------|

| QL8x12B         | 96             | 64                | 8                 | 44,68,100       | 1000            | 3000              |

| QL12x16B        | 192            | 88                | 8                 | 68,84,100       | 2000            | 6000              |

| QL16x24B        | 384            | 122               | 8                 | 84,100,144,160  | 4000            | 12000             |

| QL24x32B        | 768            | 180               | 8                 | 144, 208        | 8000            | 24000             |

See individual product data sheets for specific information on each device.

FIGURE 6a pASIC 1 Family Members

FIGURE 6b pASIC 1 Family Members

= I/O / High-drive Input / Clock Cells

□ = Logic Cells

+ = Interconnect Wiring Channels

# 24x32

# 16x24

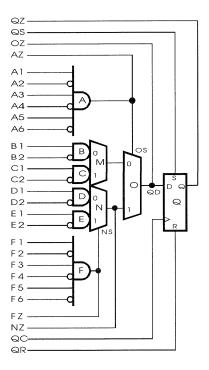

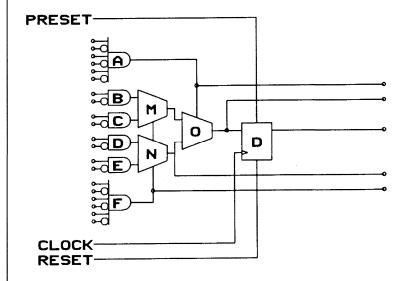

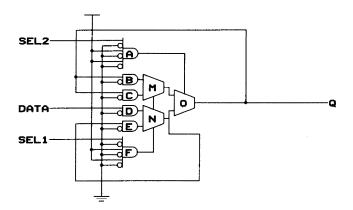

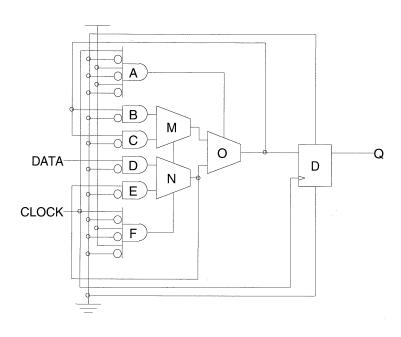

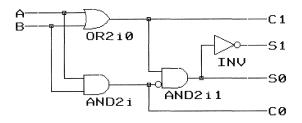

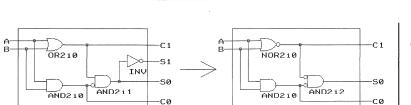

### pasic 1 internal Logic cell

The pASIC 1 internal logic cell, shown in Figure 7, is a general-purpose building block that can implement most TTL and gate array macro library functions. It has been optimized to maintain the inherent speed advantage of the ViaLink technology while ensuring maximum logic flexibility.

The logic cell consists of two 6-input AND gates, four 2-input AND gates, three 2-to-1 multiplexers and a D flip-flop. In addition to the dedicated flip-flop, logic gates in each cell can be configured to provide two latches. As noted above, each cell represents approximately 30 gate-equivalents of logic capability. Multiple outputs from the logic cell allow the automatic place and route software to pack unrelated logic functions into a single cell to maximize silicon utilization.

The pASIC 1 logic cell is unique among FPGA architectures in that it offers up to 14-input-wide gating functions. This allows many logic functions to be accomplished in a single cell delay that require two or more delays with other architectures. It can implement all possible Boolean transfer functions of up to three variables as well as many functions of up to 14 variables.

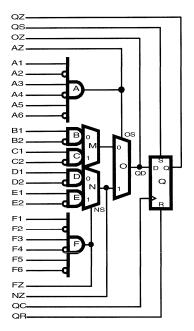

# FIGURE 7 pASIC 1 Internal Logic Cell

# **pASIC 1 FAMILY**

Glitch-free switching of the multiplexer is ensured as the internal capacitance of the circuit maintains enough charge to hold the output in a steady state during input transitions. The multiplexer output feeds the D-type flip-flop which can also be configured to provide J-K, S-R, or T-type functions as well as count with carryin. Two independent SET and RESET inputs can be used to asynchronously control the output condition. The combination of wide gating capability and a built-in sequential function makes the pASIC 1 logic cell particularly well suited to the design of high-speed state machines, shift registers, encoders, decoders, arbitration and arithmetic logic, as well as a wide variety of counters.

The function of a logic cell is determined by the logic levels applied to the inputs of the AND gates. ViaLink sites located on signal wires tied to the gate inputs perform the dual role of configuring the logic function of a cell and establishing connections between cells.

The pASIC 1 macro library contains more than 400 of the most frequently used logic functions optimized to fit the logic cell architecture. A detailed understanding of the logic cell is therefore not necessary to design successfully with pASIC 1 devices. CAE tools will automatically translate a conventional logic schematic into a device and provide excellent performance and utilization.

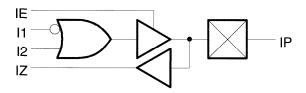

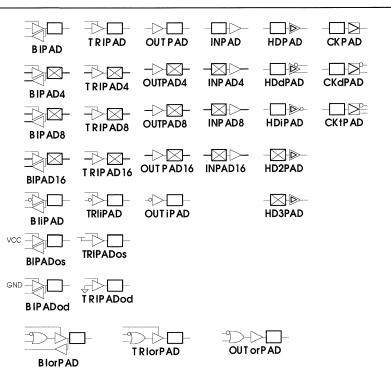

Three types of input and output structures are provided on pASIC 1 devices to configure buffering functions at the external pads. They are the Bidirectional Input/Output (I/O) cell, the Dedicated Input (I) cell and the Clock Input cell (I/CLK).

The bidirectional I/O cell, shown in Figure 8, consists of a 2-input OR gate connected to a pin buffer driver. The buffer output is controlled by a three-state enable line to allow the pad to also act as an input. The output may be configured as active HIGH, active LOW, or as an open drain inverting buffer.

The output buffers (IOL/IOH of 8 mA) are designed to ensure quiet switching characteristics while maintaining high speed. Measured results show up to 48 outputs switching simultaneously into a 10 pF load with less than  $\pm 1$  volt of output switching noise.

INPUT AND OUTPUT CELLS

FIGURE 8

Bidirectional

I/O Cell

# FIGURE10a Dedicated Input High-Drive Cell

The Dedicated Input I cell, Figure 10a, conveys true and complement signals from the input pads into the array of logic cells. As these pads have nearly twice the current drive capability of the I/O pads, they are useful for distributing high fanout signals across the device. The Clock Input I/CLK cell (Figure 10b) drives a low-skew, fanout-independent clock tree that can connect to the clock, set, or reset inputs of the flip-flop. The QL12x16B device, for example, has 80 I/O cells, 6 I cells, and 2 I/CLK cells.

# FIGURE10b Clock Input Cell

# FIGURE 11 pASIC 1 Device Features

Multiple logic cells can be programmed to form a complex logic function by interconnection through the routing channels. To describe the organization of these routing channels, a hypothetical 14-pin function consisting of two logic cells is shown in Figure 11. This device contains the same architectural features as the members of the pASIC 1 family.

Clock Wires and Quad Wires (QL16x24B and QL24x32B only). Segmented wires are predominantly used for local connections and have a ViaLink element, known as a Cross Link (denoted by the open box symbol) at every crossover point. They may also be connected to the segmented wires of cells above and below through ViaLink elements, called Pass Links (denoted by the X symbol). Express lines are similar to segmented wires except that they are not divided by pass links.

Dedicated Clock wires are lightly loaded with only three links per cell to distribute high-speed clock edges to the flip-flop CLK, SET and RESET pins. Express wires may also be used to deliver clock signals into the multiplexer region of the cell for combinatorial gating. Quad wires are similar to segmented wires in that they are employed for local interconnect, but instead of having Pass Links above and below each cell, they have Pass Links every fourth logic cell. The automatic place and route software allocates signals to the appropriate wires to ensure the optimum speed/density combination.

Horizontal wiring channels, called rows, provide connections via cross links to other columns of logic cells and to the periphery of the chip. Appropriate programming of ViaLink elements allows electrical connection to be made from any logic cell output to the input of any other logic or I/O cell. Ample wires are provided in the channels to permit automatic place and route of many designs using up to 100% of the device logic cells. Designs can be completed automatically even with a high percentage of fixed user placement of internal cells and pin locations.

The pASIC 1 Family is based on a 0.65 micron high-volume CMOS fabrication process with the ViaLink programmable-via antifuse technology inserted between the metal deposition steps. Devices from this base CMOS process have been qualified to meet the requirements of MIL-STD-883D, Revision B.

The ViaLink element exists in one of two states: a highly resistive unprogrammed, OFF, state and the low impedance, conductive, ON, state. It is connected between the output of one logic cell and the inputs of other logic cells directly or through other links. No D.C. current flows through either a programmed or an unprogrammed link during operation as a logic device. An unprogrammed link sees a worst case voltage equal to VCC biased across its terminals. A programmed link carries A.C. current caused by charging and discharging of device and interconnect capacitances during switching.

Studies of test structures and complete pASIC 1 devices have shown that an unprogrammed link under VCC bias remains in the unprogrammed state over time. Similar tests on programmed links under current bias exhibit the same stability. These tests indicate that the long term reliability of the combined CMOS and ViaLink structure is similar to that of the base gate array process. For further details see the pASIC 1 Family Reliability Report.

### RELIABILITY

### QL8X12B WildCat 1000 Very-High-Speed 1K (3K) Gate CMOS FPGA

Rev A

### pASIC HIGHLIGHTS

...1000 <u>usable</u> gates, 64 I/O pins

- Very High Speed ViaLink<sup>TM</sup> metal-to-metal programmable—via antifuse technology, allows counter speeds over 150 MHz and logic cell delays of under 2 ns.

- High Usable Density An 8-by-12 array of 96 logic cells provides 3,000 total available gates, with 1000 typically usable "gate array" gates in 44-pin and 68-pin PLCC, 68-pin CPGA, and 100-pin TOFP packages.

- Low-Power, High-Output Drive Standby current typically 2 mA. A 16-bit counter operating at 100 MHz consumes less than 50 mA. Minimum IOL of 12 mA and IOH of 8 mA

- Low-Cost, Easy-to-Use Design Tools Designs entered and simulated using QuickLogic's new QuickWorks<sup>TM</sup> development environment, or with third-party CAE tools including Viewlogic, Synopsys, Mentor, Cadence and Intergraph. Fast, fully automatic place and route on PC and workstation platforms using QuickLogic software.

### QL8x12B Block Diagram

96 Logic Cells

■ Up to 56 prog. I/O cells, 6 Input high-drive cells, 2 Input/Clk (high-drive) cells

### PRODUCT SUMMARY

The QL8x12B is a member of the pASIC 1 Family of very-high-speed CMOS user-programmable ASIC devices. The 96 logic cell field-programmable gate array (FPGA) offers 1,000 usable "gate array" gates (equivalent to 3,000 gate claims of some vendors) of high-performance general-purpose logic in 44-pin and 68-pin PLCC packages, 68-pin CPGA, and 100-pin TQFP packages.

Low-impedance, metal-to-metal, ViaLink interconnect technology provides nonvolatile custom logic capable of operating above 150 MHz. Logic cell delays under 2 ns, combined with input delays of under 1.5 ns and output delays under 3 ns, permit high-density programmable devices to be used with today's fastest CISC and RISC microprocessors and DSPs.

Designs are entered into the QL8x12B using a pASIC Toolkit which combines third-party design entry and simulation tools with QuickLogic's SpDE device-specific place & route and programming software. Ample on-chip routing channels are provided to allow fast, fully automatic place and route of designs using up to 100% of the logic and I/O cells, while maintaining fixed pin-outs.

### **FEATURES**

### Total of 64 I/O pins

- 56 Bidirectional Input/Output pins

- 6 Dedicated Input/High-Drive pins

- 2 Clock/Dedicated input pins with fanout-independent, low-skew clock networks

- Input + logic cell + output delays under 6 ns

- Chip-to-chip operating frequencies up to 110 MHz

- ✓ Internal state machine frequencies up to 150 MHz

- $\mathbf{X}$  Clock skew < 0.5 ns

- Input hysteresis provides high noise immunity

- Built-in scan path permits 100% factory testing of logic and I/O cells and functional testing with Automatic Test Vector Generation (ATVG) software after programming

- Available packages are 44- and 68-pin PLCC, 68-pin CPGA, and a 100-pin TQFP

- 68-pin PLCC compatible with QL12x16B

- 100-pin TQFP compatible with QL12x16B and QL16x24B

- 0.65μ CMOS process with ViaLink programming technology

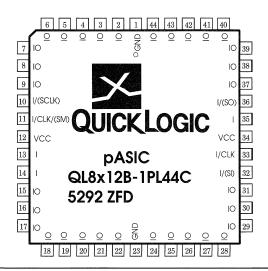

Pinout Diagram 44-pin PLCC

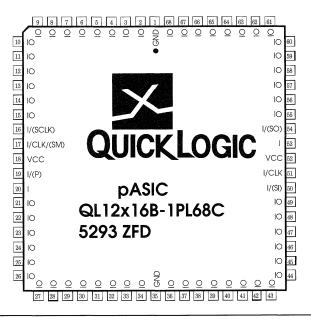

10 10 60 11 10 10 12 Ю Ю 13 Ю Ю 14 Ю Ю 15 Ю 10 I/(S CLK) QUICKLOGIC I/(S O) I/CLK/(SM) 18 VCC VCC 19 I/CLK **pASIC** 20 I/(SI) QL8x12B-1PL68C 21 Ю Ю 49 22 5293 ZFD 10 10 23 Ю Ю 24 Ю 10 25 10 10 10  $\circ \circ \circ$ 27 28 29 30 31 32 33 34

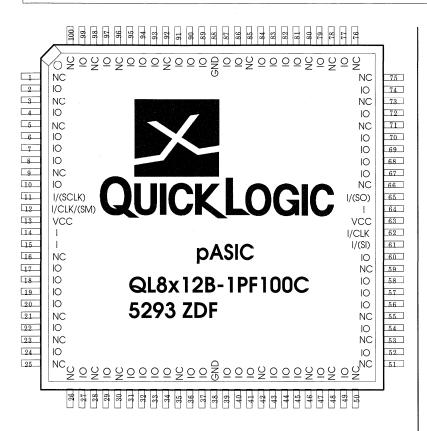

Pinout Diagram 68-pin PLCC

Pins identified I/SCLK, SM, SO and SI are used during scan path testing operation.

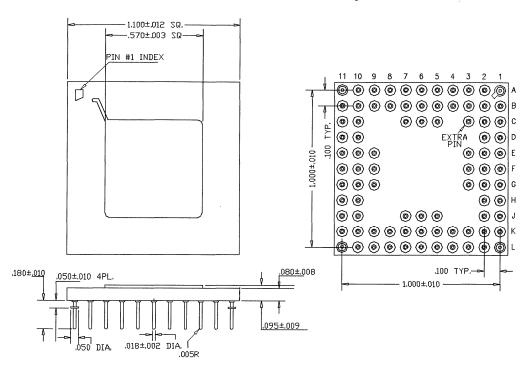

# Pinout Diagram 68-pin CPGA

### **CPGA 68 Function/Connector Pin Table**

| PIN        | FUNC       | PIN | FUNC | PIN        | FUNC   | PIN | FUNC |

|------------|------------|-----|------|------------|--------|-----|------|

| B10        | Ю          | B2  | Ю    | K2         | IO     | K10 | Ю    |

| A10        | Ю          | B1  | Ю    | L2         | Ю      | K11 | Ю    |

| В9         | Ю          | C2  | Ю    | K3         | IO     | J10 | IO   |

| <b>A</b> 9 | Ю          | C1  | Ю    | L3         | Ю      | J11 | Ю    |

| В8         | Ю          | D2  | Ю    | K4         | Ю      | H10 | Ю    |

| A8         | Ю          | D1  | Ю    | L4         | IO     | H11 | Ю    |

| В7         | I/(SCLK)   | E2  | Ю    | K5         | I/(SI) | G10 | Ю    |

| A7         | I/CLK/(SM) | E1  | Ю    | L5         | I/CLK  | G11 | IO   |

| В6         | VCC        | F2  | GND  | K6         | VCC    | F10 | GND  |

| A6         | I          | F1  | Ю    | L6         | I      | F11 | Ю    |

| В5         | I          | G2  | Ю    | K7         | I/(SO) | E10 | Ю    |

| A5         | Ю          | G1  | IO   | L7         | IO     | E11 | IO   |

| B4         | Ю          | H2  | Ю    | K8         | IO     | D10 | IO   |

| A4         | IO         | H1  | Ю    | L8         | IO     | D11 | IO   |

| В3         | Ю          | J2  | Ю    | <b>K</b> 9 | IO     | C10 | Ю    |

| A3         | Ю          | J1  | Ю    | L9         | IO     | C11 | IO   |

| A2         | IO         | K1  | IO   | L10        | IO     | B11 | Ю    |

### Pinout Diagram 100-pin TQFP

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage     | 0.5 to 7.0V      |

|--------------------|------------------|

| Input Voltage      | 0.5 to VCC +0.5V |

| ESD Pad Protection | ±2000V           |

| DC Input Current   | ±20 mA           |

| Latch-up Immunity  |                  |

| Storage Temperature |       |

|---------------------|-------|

| Ceramic65°C to +    | 150°C |

| Plastic –40°C to +  | 125°C |

| Lead Temperature    | 300°C |

#### **OPERATING RANGE**

| Cumbal | Davamatav           |                | Mili | Military |     | Industrial |      | Commercial |      |

|--------|---------------------|----------------|------|----------|-----|------------|------|------------|------|

| Symbol | Pa                  | Parameter      |      | Max      | Min | Max        | Min  | Max        | Unit |

| VCC    | Supply Voltag       | е              | 4.5  | 5.5      | 4.5 | 5.5        | 4.75 | 5.25       | V    |

| TA     | Ambient Temperature |                | -55  |          | -40 | 85         | 0    | 70         | °C   |

| TC     | Case Temperature    |                |      | 125      |     |            |      |            | °C   |

|        |                     | -X Speed Grade | 0.39 | 3.00     | 0.4 | 2.75       | 0.46 | 2.55       |      |

| V      | Dalass Factors      | -0 Speed Grade | 0.39 | 1.82     | 0.4 | 1.67       | 0.46 | 1.55       |      |

| K      | Delay Factor        | -1 Speed Grade | 0.39 | 1.56     | 0.4 | 1.43       | 0.46 | 1.33       |      |

|        | -2 Speed Grade      |                |      |          | 0.4 | 1.35       | 0.46 | 1.25       |      |

DC CHARACTERISTICS over operating range

| Symbol | Parameter                        | Conditions           | Min     | Max | Unit |

|--------|----------------------------------|----------------------|---------|-----|------|

| VIH    | Input HIGH Voltage               |                      | 2.0     |     | V    |

| VIL    | Input LOW Voltage                |                      |         | 0.8 | V    |

|        | _                                | IOH = -4  mA         | 3.7     |     | V    |

| VOH    | Output HIGH Voltage              | IOH = -8  mA         | 2.4     |     | V    |

|        | -                                | IOH = -10 μA         | VCC-0.1 |     | V    |

| VOL    | Output I OW Valtage              | IOL = 12 mA*         |         | 0.4 | V    |

| VOL    | Output LOW Voltage               | IOL = 10 μA          |         | 0.1 | V    |

| 11     | Input Leakage Current            | VI = VCC or GND      | -10     | 10  | μΑ   |

| IOZ    | 3-State Output Leakage Current   | VI = VCC or GND      | -10     | 10  | μA   |

| CI     | Input Capacitance [1]            |                      |         | 10  | pF   |

| ios    | Output Short Circuit Current [2] | VO = GND             | -10     | -80 | mA   |

| 103    | Output Short Circuit Current [2] | VO = VCC             | 30      | 140 | mA   |

| ICC    | Supply Current [3]               | VI, VIO = VCC or GND |         | 10  | mA   |

<sup>\*</sup>IOL = 12 mA for commercial range only. IOL = 8 mA for the industrial and military ranges.

- [1] Capacitance is sample tested only. CI = 20 pF max on I/(SI).

- [2] Only one output at a time. Duration should not exceed 30 seconds.

- [3] For AC conditions use the formula described in the Data Book, Section 5 Power vs Operating Frequency.

- [4] Stated timing for worst case Propagation Delay over process variation at VCC=5.0V and TA=25°C. Multiply by the appropriate Delay Factor, K, for speed grade, voltage and temperature settings as specified in the Operating Range.

- [5] These limits are derived from a representative selection of the slowest paths through the pASIC logic cell *including net delays*. Worst case delay values for specific paths should be determined from timing analysis of your particular design.

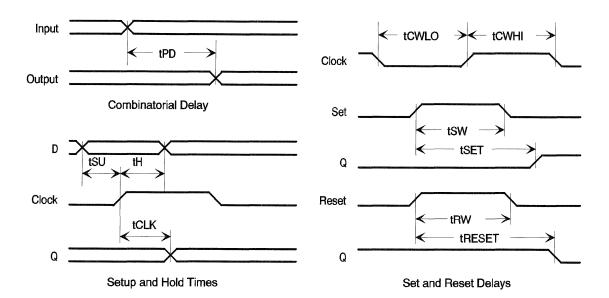

### AC CHARACTERISTICS at VCC = 5V, TA = $25^{\circ}$ C (K = 1.00)

### **Logic Cell**

|        |                         |     | ropagat | ion Delay | /s (ns) [4 | ]   |  |  |  |

|--------|-------------------------|-----|---------|-----------|------------|-----|--|--|--|

| Symbol | Symbol Parameter        |     |         | Fanout    |            |     |  |  |  |

|        |                         | 1   | 2       | 3         | 4          | 8   |  |  |  |

| tPD    | Combinatorial Delay [5] | 1.7 | 2.1     | 2.6       | 3.0        | 4.8 |  |  |  |

| tSU    | Setup Time [5]          | 2.1 | 2.1     | 2.1       | 2.1        | 2.1 |  |  |  |

| tH     | Hold Time               | 0.0 | 0.0     | 0.0       | 0.0        | 0.0 |  |  |  |

| tCLK   | Clock to Q Delay        | 1.0 | 1.5     | 1.9       | 2.3        | 4.2 |  |  |  |

| tCWHI  | Clock High Time         | 2.0 | 2.0     | 2.0       | 2.0        | 2.0 |  |  |  |

| tCWLO  | Clock Low Time          | 2.0 | 2.0     | 2.0       | 2.0        | 2.0 |  |  |  |

| tSET   | Set Delay               | 1.7 | 2.1     | 2.6       | 3.0        | 4.8 |  |  |  |

| tRESET | Reset Delay             | 1.5 | 1.8     | 2.2       | 2.5        | 3.9 |  |  |  |

| tSW    | Set Width               | 1.9 | 1.9     | 1.9       | 1.9        | 1.9 |  |  |  |

| tRW    | Reset Width             | 1.8 | 1.8     | 1.8       | 1.8        | 1.8 |  |  |  |

### **Input Cells**

| Symbol | Parameter                             | Propagation Delays (ns) [4] |     |     |     |     |     |  |  |

|--------|---------------------------------------|-----------------------------|-----|-----|-----|-----|-----|--|--|

| Cymbol | T diamotor                            | 1                           | 2   | 3   | 4   | 6   | 8   |  |  |

| tIN    | High Drive Input Delay [6]            | 2.1                         | 2.2 | 2.3 | 2.4 | 2.6 | 2.9 |  |  |

| tINI   | High Drive Input, Inverting Delay [6] | 2.1                         | 2.2 | 2.3 | 2.5 | 2.8 | 3.1 |  |  |

| tIO    | Input Delay (bidirectional pad)       | 1.4                         | 1.8 | 2.2 | 2.6 | 3.4 | 4.2 |  |  |

| tGCK   | Clock Buffer Delay [7]                | 2.7                         | 2.7 | 2.8 | 2.9 | 3.0 |     |  |  |

| tGCKHI | Clock Buffer Min High [7]             | 2.0                         | 2.0 | 2.0 | 2.0 | 2.0 |     |  |  |

| tGCKLO | Clock Buffer Min Low [7]              | 2.0 2.0 2.0 2.0 2.0         |     |     |     |     |     |  |  |

### **Output Cell**

| Symbol | Parameter                          |                   | Propagation Delays (ns) [4] Output Load Capacitance (pF) |     |     |     |  |  |

|--------|------------------------------------|-------------------|----------------------------------------------------------|-----|-----|-----|--|--|

|        |                                    | 30                | 50                                                       | 75  | 100 | 150 |  |  |

| tOUTLH | Output Delay Low to High           | 2.7               | 3.4                                                      | 4.2 | 5.0 | 6.7 |  |  |

| tOUTHL | Output Delay High to Low           | 2.8 3.7 4.7 5.6 7 |                                                          |     |     | 7.6 |  |  |

| tPZH   | Output Delay Tri-state to High     | 4.0               | 4.9                                                      | 6.1 | 7.3 | 9.7 |  |  |

| tPZL   | Output Delay Tri-state to Low      | 3.6               | 4.2                                                      | 5.0 | 5.8 | 7.3 |  |  |

| tPHZ   | Output Delay High to Tri-state [8] | 2.9               |                                                          |     |     |     |  |  |

| tPLZ   | Output Delay Low to Tri-state [8]  | 3.3               |                                                          |     |     |     |  |  |

- [6] See High Drive Buffer Table for more information.

- [7] Clock buffer fanout refers to the maximum number of flip flops per half column. The number of half columns used does not affect clock buffer delay.

- [8] The following loads are used for tPXZ:

### **High Drive Buffer**

|        |                                      | Clock Drivers                   | Propagation Delays (ns) [4] Fanout |     |     |     |     |  |

|--------|--------------------------------------|---------------------------------|------------------------------------|-----|-----|-----|-----|--|

| Symbol | Parameter                            | Clock Drivers<br>Wired Together |                                    |     |     |     |     |  |

|        |                                      | wired rogether                  | 12                                 | 24  | 48  | 72  | 96  |  |

|        |                                      | 1                               | 4.0                                | 4.9 |     |     |     |  |

| +181   | tIN High Drive Input Delay           | 2                               |                                    | 3.5 | 5.0 |     |     |  |

| LIIN   |                                      | 3                               |                                    |     | 4.0 | 4.8 | 5.6 |  |

|        |                                      | 4                               |                                    |     |     | 4.1 | 4.8 |  |

|        |                                      | 1                               | 4.2                                | 5.1 |     |     |     |  |

| +1511  | High Drive Input,                    | 2                               |                                    | 3.7 | 5.2 |     |     |  |

| tINI   | High Drive Input,<br>Inverting Delay | 3                               |                                    |     | 4.2 | 5.0 | 5.8 |  |

|        |                                      | 4                               |                                    |     |     | 4.3 | 5.0 |  |

#### **AC Performance**

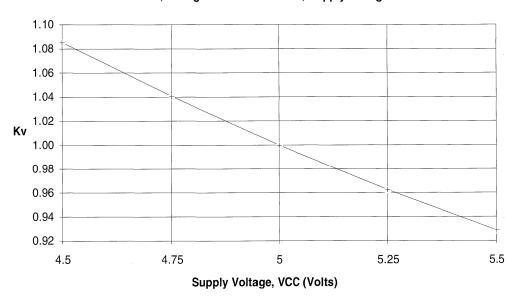

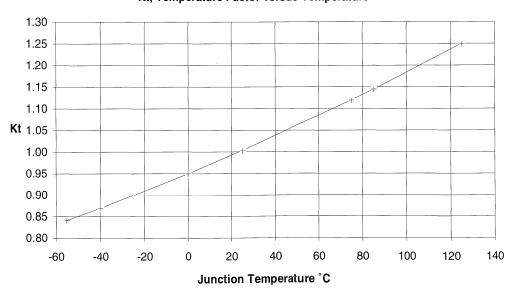

Propagation delays depend on routing, fanout, load capacitance, supply voltage, junction temperature, and process variation. The AC Characteristics are a design guide to provide initial timing estimates at nominal conditions. Worst case estimates are obtained when nominal propagation delays are multiplied by the appropriate Delay Factor, K, as specified in the Delay Factor table (Operating Range). The effects of voltage and temperature variation are illustrated in the graphs on page 2-55, K Factor versus Voltage and Temperature. The SpDE Toolkit incorporates data sheet AC Characteristics into the QDIF database for pre-place-and-route timing analysis. The SpDE Delay Modeler extracts specific timing parameters for precise path analysis or simulation results following place and route. For definition of timing parameters, see page 2-56, Timing Waveforms.

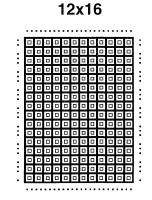

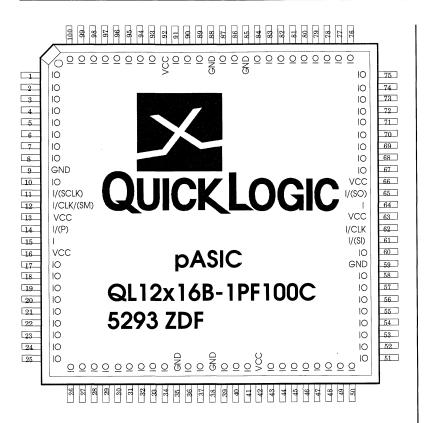

### QL12x16B WildCat 2000 Very-High-Speed 2K (6K) Gate CMOS FPGA

Rev A

### pASIC HIGHLIGHTS

Very High Speed − ViaLink<sup>TM</sup> metal-to-metal programmable–via antifuse technology, allows counter speeds over 150 MHz and logic cell delays of under 2 ns.

...2000 <u>usable</u> gates, 88 l/O pins

- High Usable Density A 12-by-16 array of 192 logic cells provides 6,000 total available gates, with 2000 typically usable "gate array" gates in 68-pin and 84-pin PLCC, 84-pin CPGA, 100-pin CQFP, and 100-pin TQFP packages.

- Low-Power, High-Output Drive Standby current typically 2 mA. A 16-bit counter operating at 100 MHz consumes less than 50 mA. Minimum IOL of 12 mA and IOH of 8 mA

- Low-Cost, Easy-to-Use Design Tools Designs entered and simulated using QuickLogic's new QuickWorks<sup>TM</sup> development environment, or with third-party CAE tools including Viewlogic, Synopsys, Mentor, Cadence and Intergraph. Fast, fully automatic place and route on PC and workstation platforms using QuickLogic software.

QL12x16B Block Diagram

192 Logic Cells

■ = Up to 80 prog. I/O cells, 6 Input high-drive cells, 2 Input/Clk (high-drive) cells

### PRODUCT SUMMARY

The QL12x16B is a member of the pASIC 1 Family of very-high-speed CMOS user-programmable ASIC devices. The 192 logic cell field-programmable gate array (FPGA) offers 2,000 usable "gate array" gates (equivalent to 6,000 gate claims of some vendors) of high-performance general-purpose logic in 68-pin and 84-pin PLCC packages, 84-pin CPGA, 100-pin CQFP, and 100-pin TQFP packages.

Low-impedance, metal-to-metal, ViaLink interconnect technology provides nonvolatile custom logic capable of operating above 150 MHz. Logic cell delays under 2 ns, combined with input delays of under 1.5 ns and output delays under 3 ns, permit high-density programmable devices to be used with today's fastest CISC and RISC microprocessors and DSPs.

Designs are entered into the QL12x16B using a pASIC Toolkit which combines third-party design entry and simulation tools with QuickLogic's SpDE device-specific place & route and programming software. Ample onchip routing channels are provided to allow fast, fully automatic place and route of designs using up to 100% of the logic and I/O cells, while maintaining fixed pin-outs.

#### **FEATURES**

- Total of 88 I/O pins

- 80 Bidirectional Input/Output pins

- 6 Dedicated Input/High-Drive pins

- 2 Clock/Dedicated input pins with fanout-independent, low-skew clock networks

- Input + logic cell + output delays under 6 ns

- Chip-to-chip operating frequencies up to 110 MHz

- Internal state machine frequencies up to 150 MHz

- $\mathbf{X}$  Clock skew < 0.5 ns

- Input hysteresis provides high noise immunity

- Built-in scan path permits 100% factory testing of logic and I/O cells and functional testing with Automatic Test Vector Generation (ATVG) software after programming

- Available packages are 68- and 84-pin PLCC, 84-pin CPGA, 100-pin CQFP, and a 100-pin TQFP

- 84-pin PLCC compatible with QL16X24B

- 100-pin TQFP compatible with QL8x12B and QL16x24B

- 0.65μ CMOS process with ViaLink programming technology

Pinout Diagram 68-pin PLCC

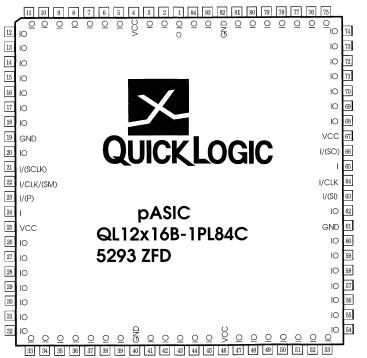

Pinout Diagram 84-pin PLCC

Pins identified I/SCLK, SM, SO and SI are used during scan path testing operation.

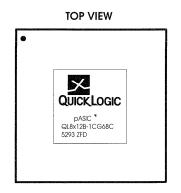

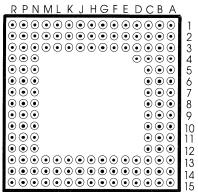

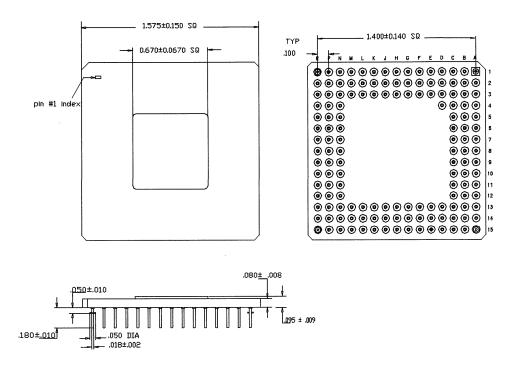

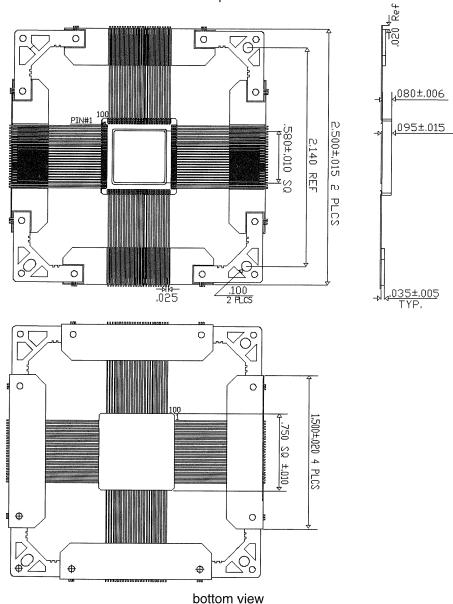

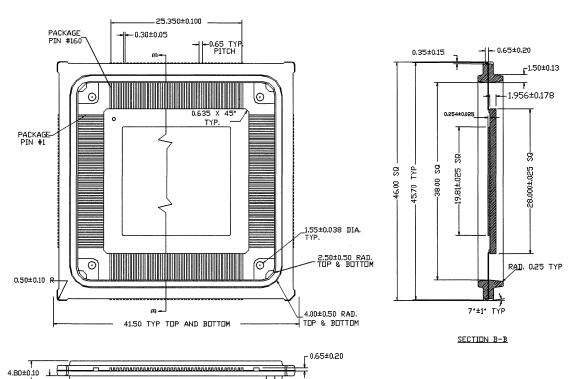

### Pinout Diagram 84-pin CPGA

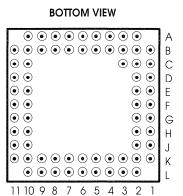

### **BOTTOM VIEW**

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul><li>•</li></ul> | 00      | • •        | 000 | 0 ( | $\odot$ $\odot$ | Α |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|------------|-----|-----|-----------------|---|

| <ul> <li>• • • • • • • • • • • • • • • • • • •</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |         |            |     |     |                 | В |